|

|

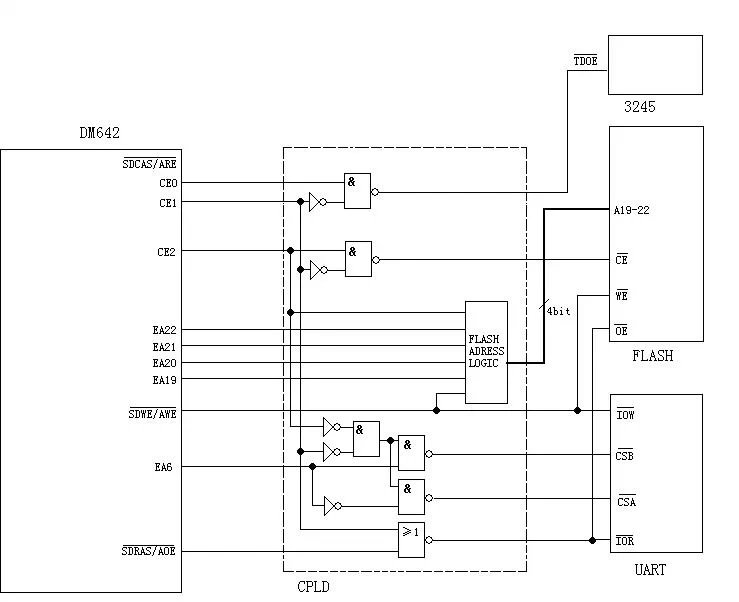

CPLD里主要譯址邏輯關(guān)系,F(xiàn)LASH地址邏輯是采用向CE2空間的高空間執(zhí)行寫操作來換頁的。例如對CE2的某空間(EA22:19=0110)寫任意數(shù)據(jù),則FLASH高4位地址切換為0110。這點與用FPGA進行選址的DM642開發(fā)板邏輯方式不同。因為管腳資源有限,又考慮信號完整性,再加上CPLD資源有限,所以數(shù)據(jù)線沒有引到CPLD,通過這個方式進行頁切換。

因為頁切換方式不同,所以FLASHBURN燒寫用到的.out文件中相關(guān)代碼要自己更改。另外超過虛擬頁512K大小的程序BOOT也要做相關(guān)的調(diào)整。

|

|