|

很多人可能覺得PCB信號速率越高,如25Gbps,56G/112G-PAM4信號等調試上發現的問題會越多,其實不然。我們收到最多的調試問題還是DDR3、DDR4等,不是跑不到額度速率,就是識別不到,或者training出現了問題。這種情況下往往調試很久也找不到問題在哪里,最后可能會懷疑是不是PCB設計哪里出了問題,因為原理方案和軟件是參考廠家的,“最不容易出錯”。 之所以說調試很麻煩,尤其是出了問題后,牽扯到的因素太多,所謂術業有專攻,我們只能從PCB設計和信號或電源完整性的角度去排除,如果涉及到硬件原理或者軟件等,我們可能也是一籌莫展。借助今天要講的這個案例,我們可以來簡單說一下在調試過程中一般會怎么處理這種DDRx問題。 某客戶在調試過程中發現他們的DDR3只能在低頻下單片正常工作,多片沒法同時正常運行,調試了好久也沒有找到問題在哪里,最后來求助我們,希望我們查一下PCB設計,或者看是否能實物測試一下信號,下面是客戶反饋的問題描述。

然后對應的測試部分結果如下,可以看到在時鐘頻率400MHz(對應數據率800Mbps)下測試了兩塊板,1號板只有A通道的第0片(挨著主芯片的第1片)顆粒通過,其余顆粒均報錯不通過。2號板只有A通道的第0,1 , 3片顆粒通過,其余均報錯不通過。如下圖片所示。

在時鐘頻率800MHz(對應數據率1600Mbps)下測試所有顆粒都報錯不通過,如下圖所示。

按照我們之前一貫的說法,如果DDRx不能跑到額定速率,通過降頻能改善的話,則說明一般是時序裕量問題,這種情況可能和PCB設計或者驅動及ODT的配置有關系,我們通過查板或者仿真有很大概率能找到并解決這類問題。 眼前的這個DDRx問題現象在高頻的時候都報錯不通過,而降頻后有部分不報錯可以通過,說明降頻后還是有改善的,于是我們讓客戶把PCB設計文件給我們查一下,這個也是我們解BUG的基本套路。

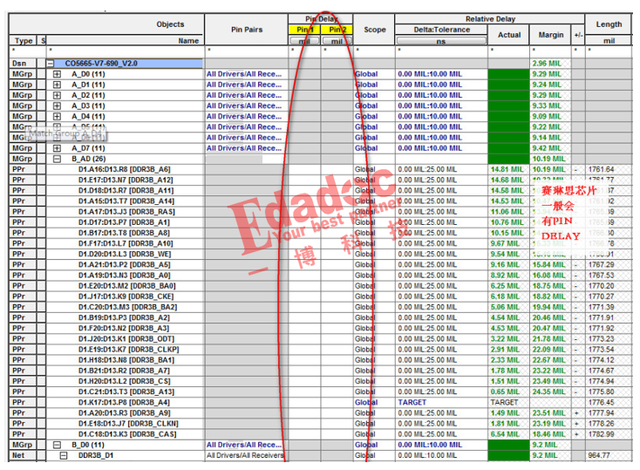

拿到PCB板子,確實也發現了不少問題,挑出下面幾個比較明顯一點的。 1、PCB做等長的時候沒有把芯片的Pin delay一起加上考慮,會影響時序;

2、電路板地址線的等長規則只設置了第一片顆粒到主控芯片的主干段,顆粒到顆粒間的分支沒有設置相關規則,會影響到時序;

3、時鐘按照Fly_by拓撲走線,端接電阻放在了靠近第1片顆粒處而不是最后一片顆粒處,這是一個嚴重的問題,如下圖所示。

看到這里,眼尖的小伙伴們可能就知道問題出在了哪里,于是我們便讓客戶快速做一個實驗,把上圖紅色圈出的電阻想辦法焊接到最后一片顆粒對應的管腳P N上,同時擔心客戶不太明白,于是好人做到底,順便把PCB對應的電阻位號和要挪到的位置也按照下圖所示標示了出來。

因為B通道也是同樣的問題,而且調試情況更糟糕,于是我們順便也讓客戶按照同樣的方法挪動了B通道的時鐘網絡電阻位置。

第二天好消息傳來,客戶按照我們的建議挪了電阻的位置,問題解決了。這個PCB板案例也說明了有時我們查板會發現很多細節不符合PCB設計要求,最重要的是要學會分析哪個點才是關鍵(致命)問題所在;同時我們發現在速率不是很高的情況下,就算不考慮芯片的pin delay,系統也不至于沒法工作,這些都是引起時序裕量不足的一些因素,而我們要做的就是盡量從各方面去摳出更多的裕量。

|