|

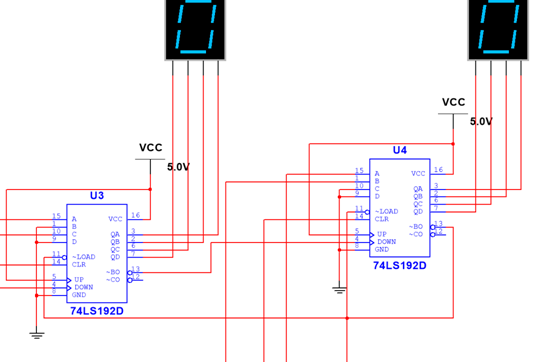

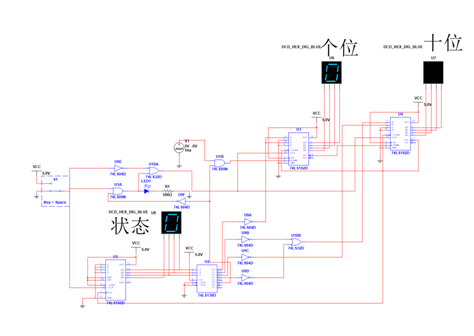

要求分析 根據任務要求,使用邏輯門電路設計一款電飯煲,主要目的: 1. 設計一款倒計時電路,最高支持倒計時20分鐘。 2. 設計一款計數器電路,最高支持4~6種不同狀態。 3. 支持根據不同狀態,設置不同倒計時參數。 二 問題分析根據項目分析可以確定該設計可以通過:信號源、減法電路、加法電路、以及相關邏輯門電路幾個部分構成。 由于項目中最小時間單位是分鐘,所以選用每一個時鐘代表一分鐘進行實驗。基本設計思路如下圖所示: 圖2.1 整體設計思路 三 設計過程3.1 倒計時設置邏輯因為在初始上電狀態下,芯片處于不穩定狀態,所以狀態標識如下所示: 0:啟動;1:預加熱5分鐘; 2: 吸水10分鐘3:加熱煮飯20分鐘;4:燜飯10分鐘;5:保溫并提示; 根據以上狀態以及要求,列出需要設定的倒計時的真值表如下所示: 表3.1 倒計時時間真值表 由于存在單獨狀體的情況且狀態的二進制表示不超過3bit,使用74LS138譯碼器能極大的減小設計難度。 根據上表,設個位十位的由低到高分別為A1、B1、C1、D1、A1、B1、C1、D1,74LS138的輸出分別為Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7則可以得出以下關系: A1= C1=Y0’ A2= Y1’ +Y3’ B2=Y2’ 圖3.1 倒計時時間設置邏輯 3.2 CLR信號處理根據74LS192和74LS160的手冊,對CLR信號進行分析。使用單刀雙擲開關作為電飯煲開關,開關置于VCC是,認為啟動,為數字邏輯1,反之置于GND則為0。開關S1=0時,所有芯片清零,S1=1時,所有倒計時結束后74LS160不置零,74LS192置零并且CLK無輸入。所以74LS192的CLR取決于S1狀態、和Y5的狀態如下表。根據分析得出CLR=Y5’S1+S1’。 表3.2 74LS192CLR引腳邏輯真值表 圖3.2 74LS192CLR引腳邏輯電路圖 3.3 CLK信號處理根據芯片手冊可知74LS160的CLK輸入可以從74LS192的~BO引腳獲取,并且個位的~BO引腳可以作為十位的74LS192CLK信號。減發器將使用異步方式遞減,個位的倒計時解釋后從十位借位,如果十位為0,則~BO引腳將輸出一個低電平。該低電平可作為74LS160的狀態轉化CLK輸入。根據以上分析可知個位的74LS194CLK還需要滿足S1=1時, 74LS192CLK無輸入,即在Y5=0時,CLK沒有輸入。將個位和十位的74LS194的CLK信號分別命名為CLK1,CLK2則CLK1真值表如下: 表3.3 CLK真值表 由此得出:CLK1= Y5CLK。電路圖如下所示: 圖3.3 個位74LS192CLK邏輯電路圖 3.4 LOAD信號處理因為默認情況下74LS192的置數是0,根據芯片時序圖可知,初始狀態下即可獲取一個借位信號,所以在初始狀態下十位的74LS192接收到個位的借位信號時,同樣需要借位,所以可以將十位的借位信號作為兩片74LS192的LOAD信號。

圖3.4 74LS192LOAD信號邏輯電路圖 74LS160由于通過CLR清零,并不需要LOAD處理,所以為保證穩定性,74LS160的LOAD信號接地。 3.5 顯示部分與報警信號顯示使用BCD八段數碼管做顯示,報警信號時在S1=1并且Y5=0時,邏輯為1,所以報警信號等于Y5’S1。 圖3.5 報警信號邏輯電路圖 四 仿真結果

圖4.1 整體電路圖上電時,若S1狀態為0,則所有芯片清零,無顯示。若S1為1,則74LS160的CLK被74LS192的借位觸發,74LS160顯示狀態1,74LS192同時被置位顯示05,CLK開始倒計時。然后倒計時結束,74LS192借位,74ls160顯示狀態2,74LS192同時被置位顯示10,然后倒計時結束,74LS192借位,74ls160顯示狀態3,74LS192同時被置位顯示20,然后倒計時結束,74LS192借位,74ls160顯示狀態4,74LS192同時被置位顯示10,然后倒計時結束,74LS192借位,74ls160顯示狀態5,74LS192同時被清零,CLK輸入被置低,顯示00,發光二極管被點亮。在該過程中任意時刻將S1置0,所有芯片立刻清零,系統復位,所有數碼管顯示0,S1重新置1后恢復以上步驟。

Multisim仿真工程文件和word下載:

電飯煲.rar

(516.49 KB, 下載次數: 0)

電飯煲.rar

(516.49 KB, 下載次數: 0)

2025-9-17 09:59 上傳

點擊文件名下載附件

包含設計思路word描述 下載積分: 黑幣 -5

|