在FPGA工程設(shè)計(jì)中,加法器的身影隨處可見(jiàn),加法器看似簡(jiǎn)單在實(shí)際的應(yīng)用中很容易出錯(cuò),尤其是在做定點(diǎn)數(shù)加法時(shí)往往會(huì)遇到?jīng)]有小數(shù)點(diǎn)位置對(duì)齊導(dǎo)致錯(cuò)誤。加法器主要可分為半加器、全加器;按操作數(shù)不同可以分定點(diǎn)數(shù)加法器、浮點(diǎn)數(shù)加法器,針對(duì)有符號(hào)無(wú)符號(hào)數(shù)也要設(shè)計(jì)不同的加法器。學(xué)習(xí)是個(gè)由淺及深循序漸進(jìn)的過(guò)程,一開(kāi)始就從最簡(jiǎn)單的半加器開(kāi)始,這里用最簡(jiǎn)單的加法器熟悉一下FPGA開(kāi)發(fā)流程,建工程的一些規(guī)范及怎樣寫(xiě)去仿真。

1.一位半加器: 電路是指對(duì)兩個(gè)輸入數(shù)據(jù)位相加,輸出一個(gè)結(jié)果位和進(jìn)位,沒(méi)有進(jìn)位輸入的加法器電路。 是實(shí)現(xiàn)兩個(gè)一位二進(jìn)制數(shù)的加法運(yùn)算電路。半加器不考慮低位的進(jìn)位

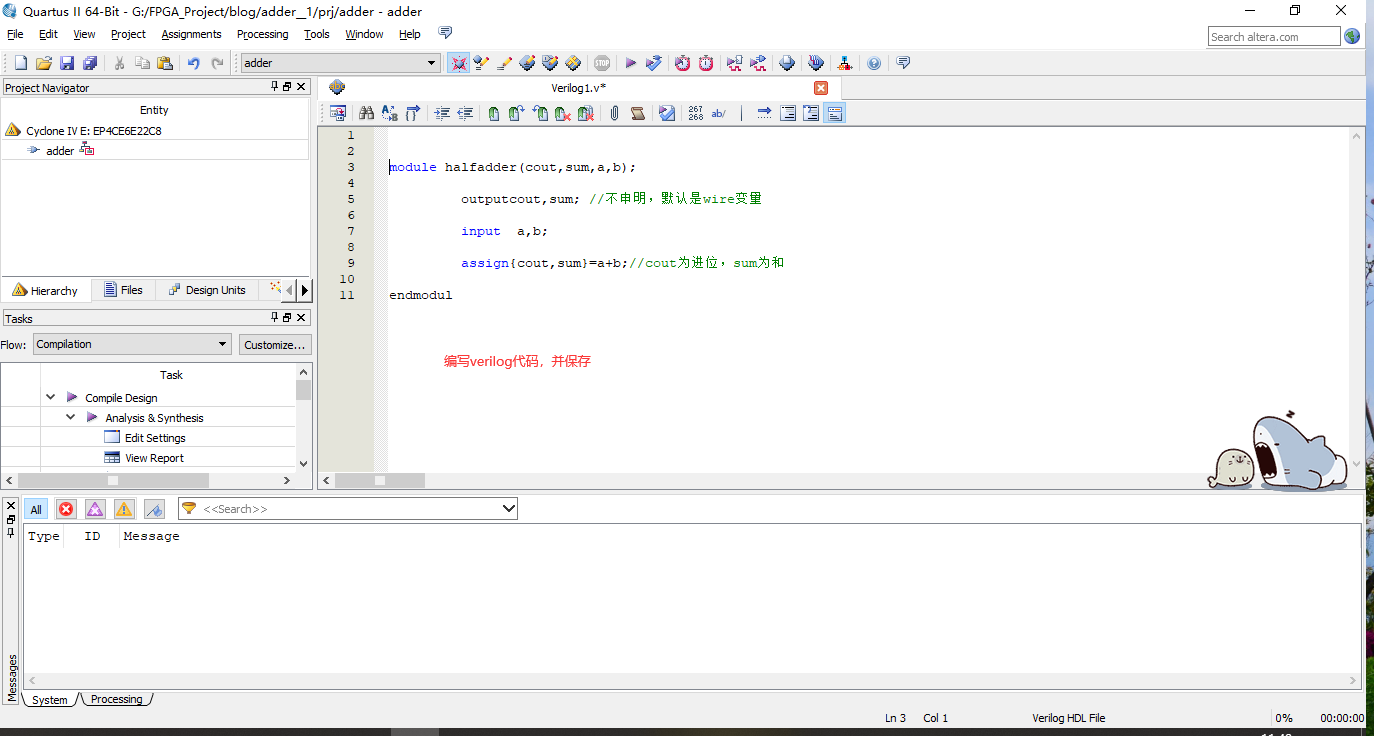

module halfadder(cout,sum,a,b);

outputcout,sum; //不申明,默認(rèn)是wire變量

input a,b;

assign{cout,sum}=a+b;//cout為進(jìn)位,sum為和

endmodul

2.全加器 :是用門(mén)電路實(shí)現(xiàn)兩個(gè)二進(jìn)制數(shù)相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進(jìn)位,并輸出本位加法進(jìn)位。多個(gè)一位全加器進(jìn)行級(jí)聯(lián)可以得到多位全加器。

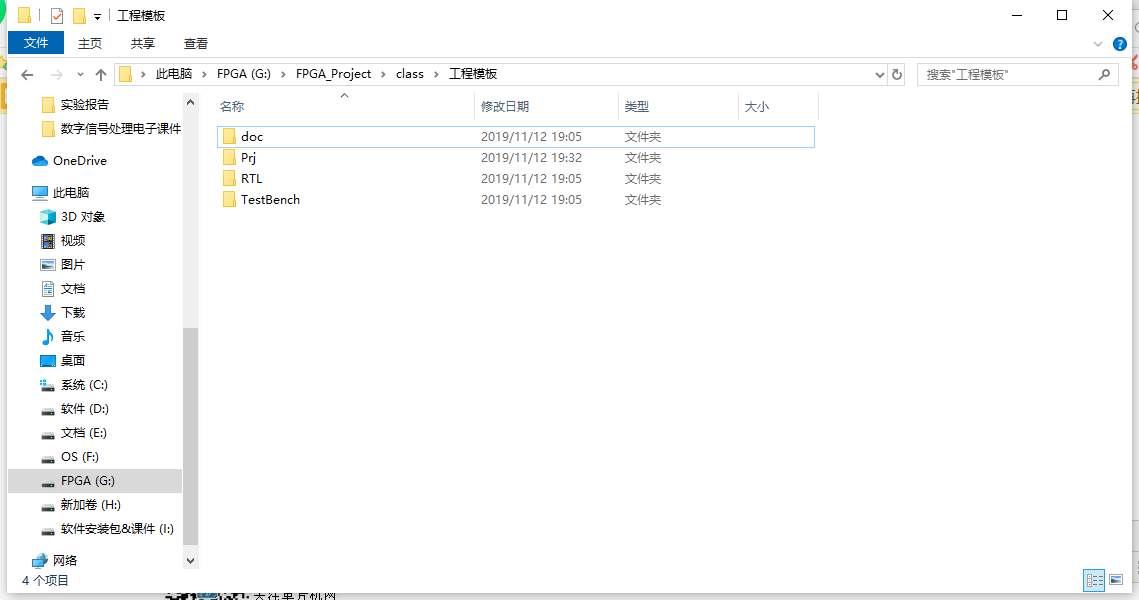

module fulladder(a,b,cin,cout,sum); inputa,b,cin; outputcout,sum; assign{cout,sum}=a+b+cin; endmodule 3.兩個(gè)半加器構(gòu)成全加器 module fulladder(x,y,c_in,sum,c_out); inputx; inputy; inputc_in; outputsum; outputc_out; wirea_sum; wirea_out; wireb_out; assignc_out=a_out|b_out; halfadderhalf(x,y,a_sum,a_out); halfadderhalf1(c_in,a_sum,sum,b_out); endmodule 第一步新建一個(gè)文件夾 建工程文件夾盡量規(guī)范,文件夾下最要包含 doc prj RTL Testbench 文件夾 doc主要放一些工程文檔 前期沒(méi)有可以空著,prj文件夾放工程,及ip核文件,RTL放模塊代碼.v文件 ,Testbench文件夾放測(cè)試激勵(lì)文件。

工程文件夾模板

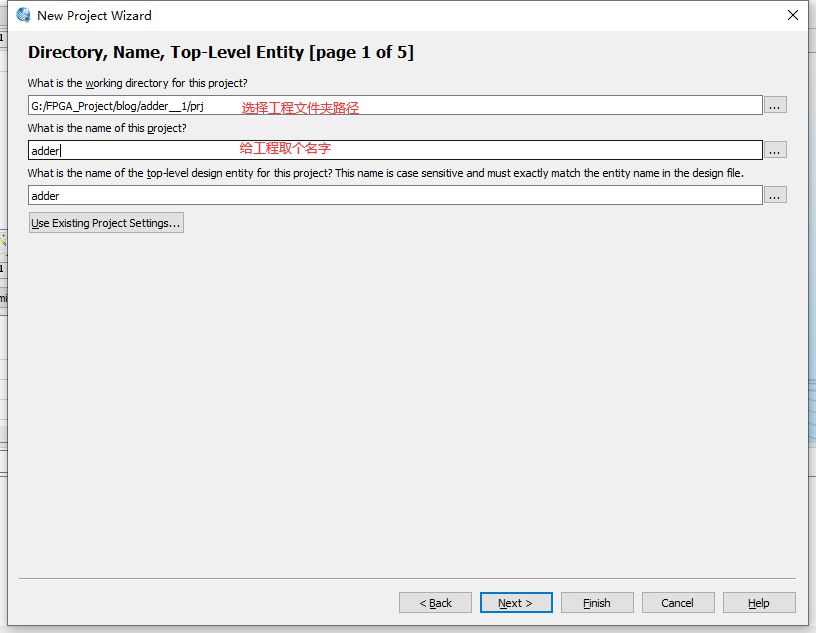

2.打開(kāi)quartus 軟件新建工程,

2.打開(kāi)quartus 軟件新建工程,

選擇路徑 并給工程命名

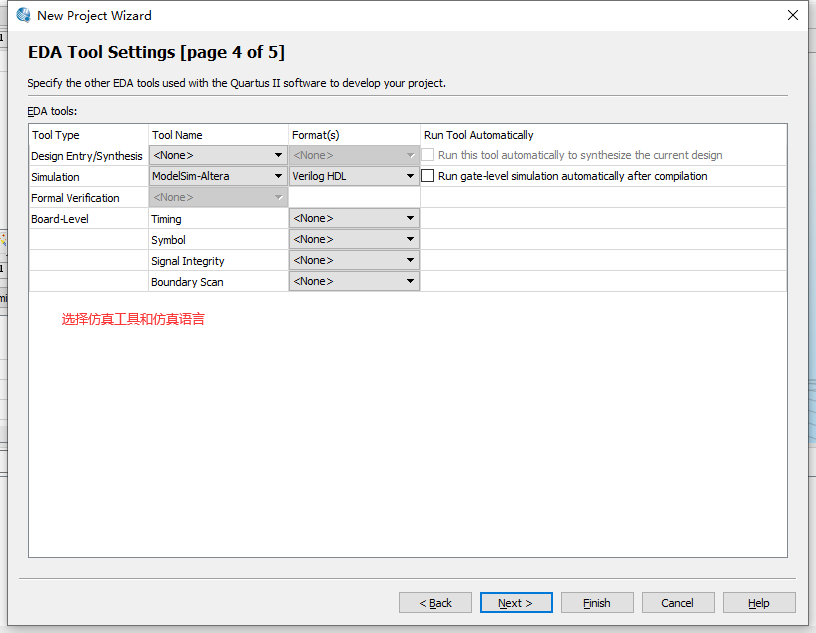

選擇仿真工具和語(yǔ)言

選擇仿真工具和 仿真語(yǔ)言

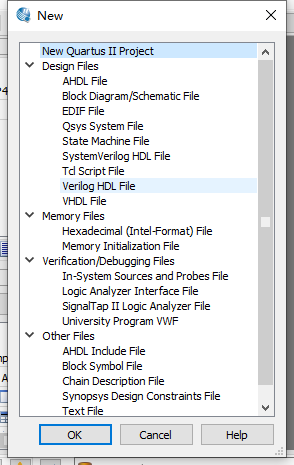

新建.v文件

新建一個(gè)verilog文件

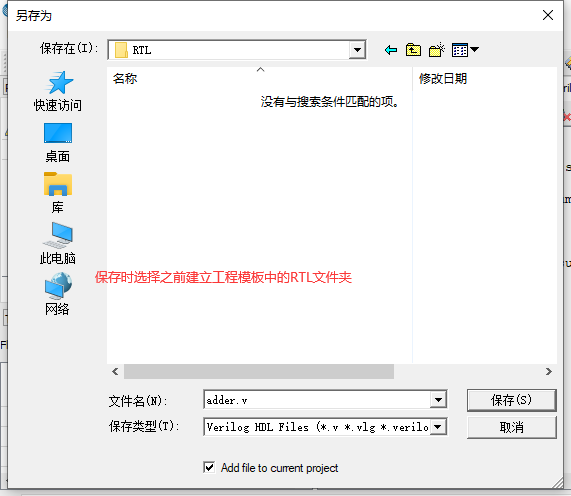

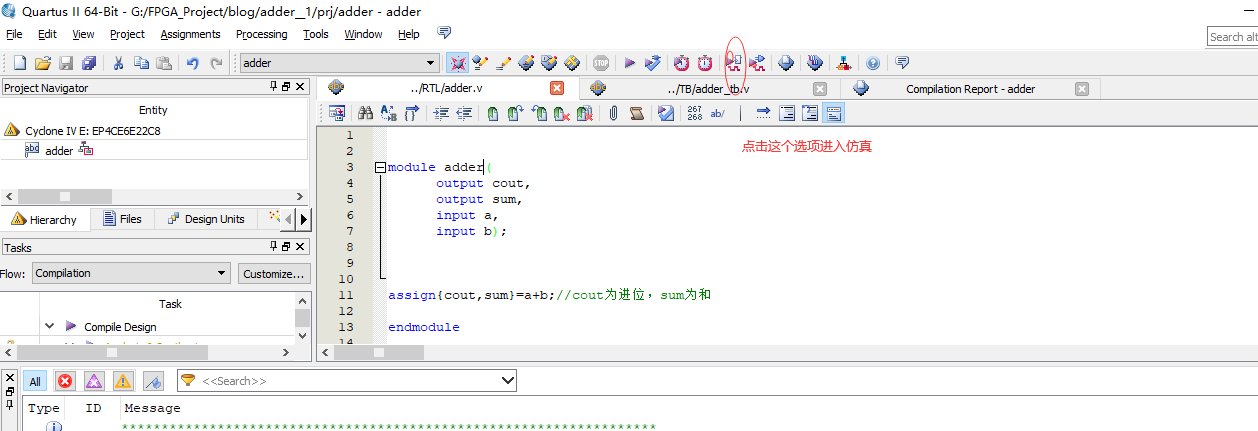

編寫(xiě)代碼并保存

將代碼保存到RTL文件夾

再新建一個(gè)verilog文件 作為T(mén)b文件 編寫(xiě)tb文件后保存到TB文件下。

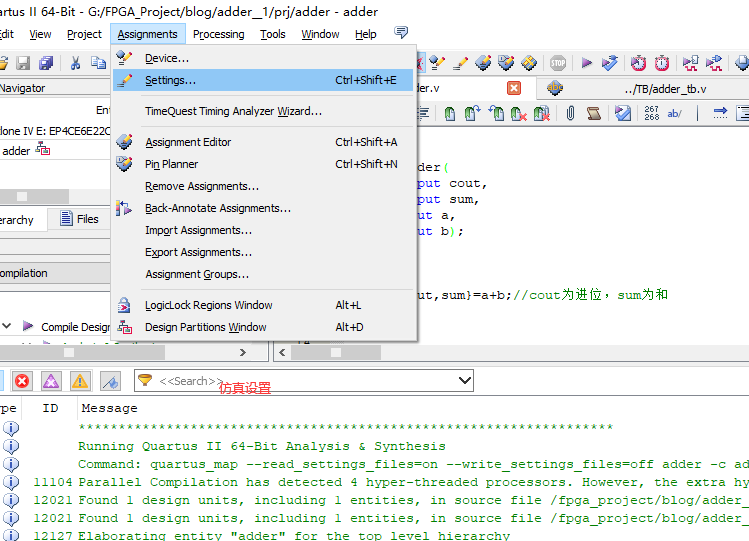

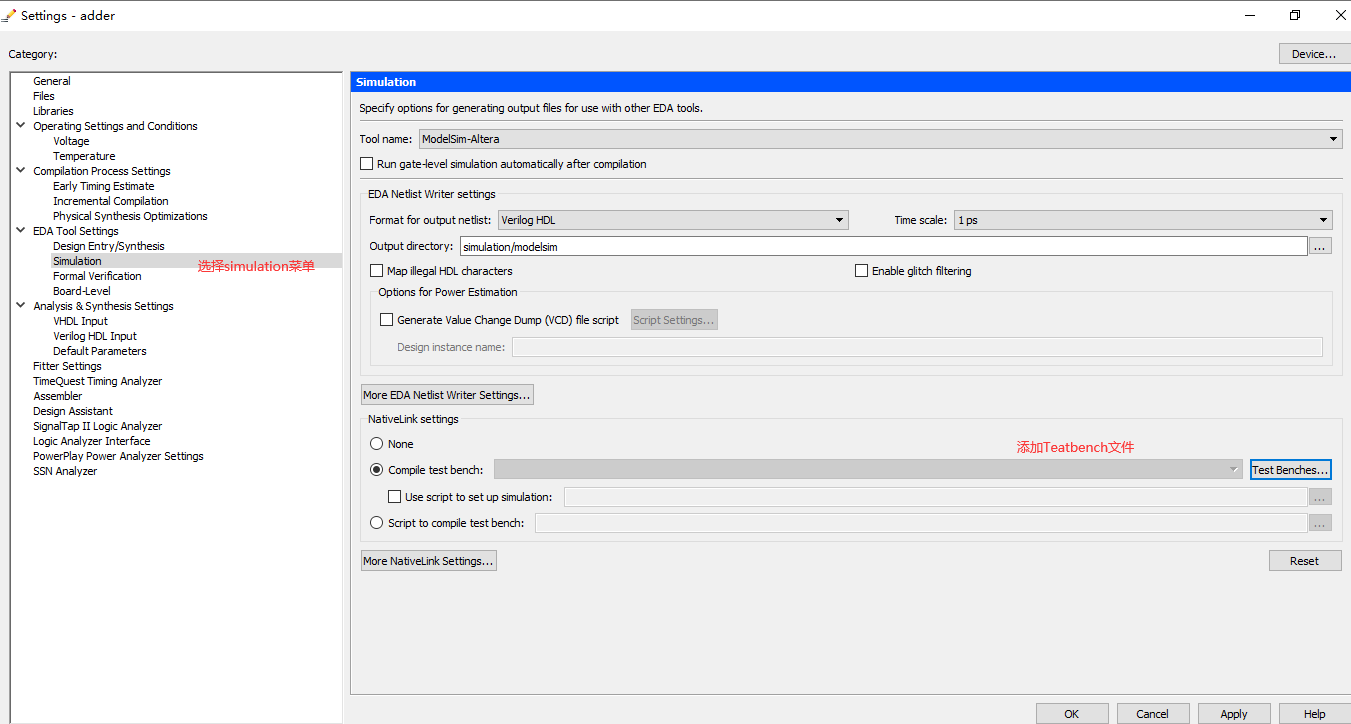

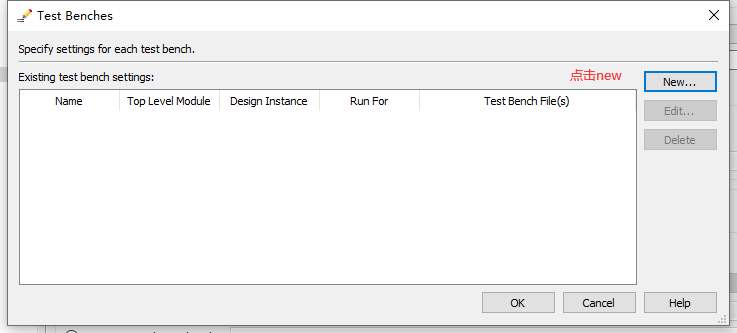

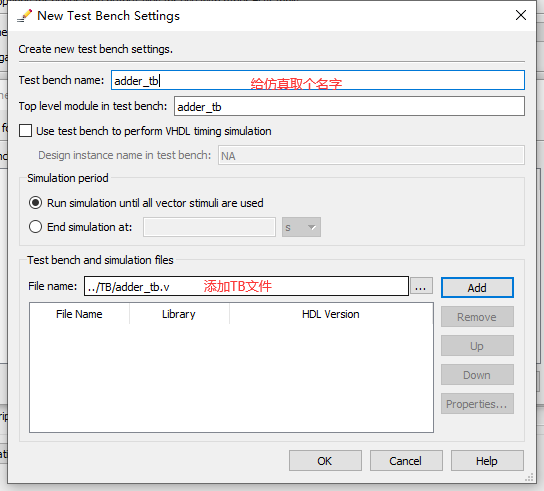

編寫(xiě)完成后需要進(jìn)行仿真設(shè)置。

選擇設(shè)置菜單

選擇simulation設(shè)置

添加TB文件

添加完成后進(jìn)行仿真

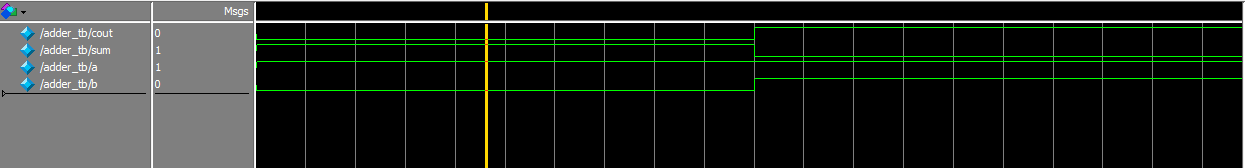

仿真結(jié)果

|