|

|

ժҪ

��������Ҫ�漰����(du��) DDR2�� DDR3���O(sh��)Ӌ(j��)ӡ�ƾ�·�壨PCB���r(sh��)�����]��̖(h��o)�����Ժ��Դ�����Ե��O(sh��)Ӌ(j��)���(xi��ng)���@Щ�Ǿ����ஔ(d��ng)�������(zh��n)�Եġ��������c(di��n)��ӑՓ�ڱM�����ٵ� PCB �Ӕ�(sh��)���e�� 4�Ӱ����r�µ����P(gu��n)���g(sh��)������һЩ�O(sh��)Ӌ(j��)��������ǰ�ѽ�(j��ng)�����ʹ���^��

1. ��B

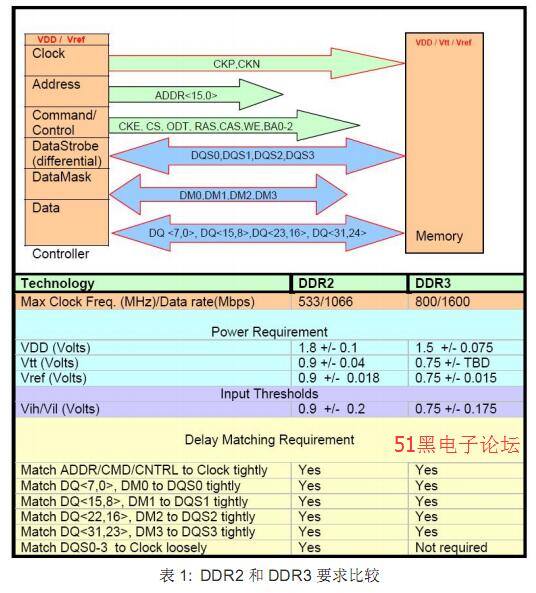

Ŀǰ�����^�ձ�ʹ���е� DDR2 ���ٶ��ѽ�(j��ng)���_(d��) 800 Mbps���������ߵ��ٶȣ��� 1066 Mbps���� DDR3���ٶ��ѽ�(j��ng)���_(d��)1600 Mbps����(du��)����˸ߵ��ٶȣ���PCB���O(sh��)Ӌ(j��)�Ƕȁ��v��Ҫ������(y��n)��ĕr(sh��)��ƥ�䣬�ԝM�㲨�ε������ԣ��@���кܶ��������Ҫ���]�����е��@Щ���ض��Ǖ�(hu��)����Ӱ푵ģ����ǣ�����֮�g߀�Ǵ���һЩ��(g��)�Եģ��������Ա���� PCB�B�ӡ��迹����(li��n)��?f��)䡢�r(sh��)��ƥ�䡢��?d��ng)_���Դ�����Ժ͕r(sh��)��Ŀǰ���кܶ� EDA���߿��Ԍ�(du��)�����M(j��n)�кܺõ�Ӌ(j��)��ͷ��棬���� Cadence ALLEGRO SI-230 �� Ansoft��s HFSSʹ�õı��^�ࡣ

������pdf��ʽ�ęn51�����d��ַ����15퓣���

ᘌ�(du��)DDR2-800��DDR3��PCB��̖(h��o)�������O(sh��)Ӌ(j��).pdf

(1.43 MB, ���d��(sh��): 36)

ᘌ�(du��)DDR2-800��DDR3��PCB��̖(h��o)�������O(sh��)Ӌ(j��).pdf

(1.43 MB, ���d��(sh��): 36)

2018-2-6 09:41 �ς�

�c(di��n)���ļ������d����

|

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664