���T�� 51��Ƭ�C(j��) | 24С�r�ش��^(q��) | ��Ƭ�C(j��)�̳� | ��Ƭ�C(j��)DIY���� | STM32 | Cortex M3 | ģ��(sh��)��� | ���DIY���� | ���/���� | ��C(j��)���@ | Arduino | Ƕ��ʽOS | �����O(sh��)Ӌ(j��)

���T�� 51��Ƭ�C(j��) | 24С�r�ش��^(q��) | ��Ƭ�C(j��)�̳� | ��Ƭ�C(j��)DIY���� | STM32 | Cortex M3 | ģ��(sh��)��� | ���DIY���� | ���/���� | ��C(j��)���@ | Arduino | Ƕ��ʽOS | �����O(sh��)Ӌ(j��)

|

| ��?d��ng)_ ����Ƚ��� |

| ��(y��ng)ԓ���S�Ҽ��g(sh��)�ˆT |

| �@�N���}�����x��ľ��w��S�Ĺ�ˇ���}����(y��ng)ԓ���S�Ҽ��g(sh��)�ˆT����Փ���톖�]�����x�� |

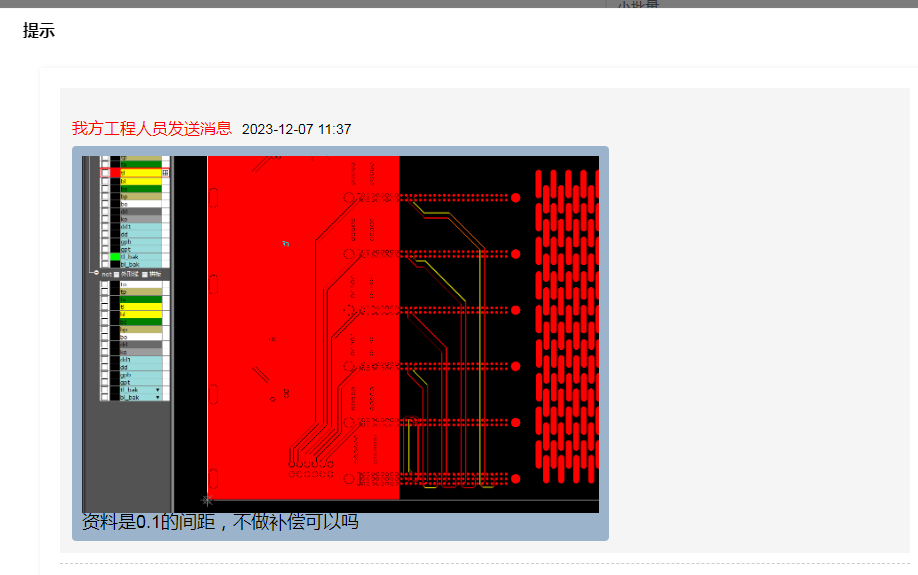

| ��ւ�ݔ�����g������PCB��Printed Circuit Board��ӡˢ�·�壩�O(sh��)Ӌ(j��)�dz���Ҫ����?y��n)���ֱ��Ӱ푵���̖�����ܡ����ɔ_�����Լ�����늴ż����ԣ�EMC����ͨ������־����g��������(j��)�O(sh��)Ӌ(j��)Ҫ����̖�l�ʺ��ض���(y��ng)�ö������{(di��o)���� ��һ����r�£���־����g������O(sh��)�Þ���֮�g�����ĵ����ľ��x�����ںܶ���ٲ����̖����Ҋ�IJ�־��g�������0.1 mm��0.2 mm֮�g���@�NС�g�������Ч�pС�����̖֮�g�Ļ��У������̖�����ԣ��e���ڸ��l�ʻ���ٲ����̖��ݔ�С� ���M(j��n)�в�־����֕r��Ո���]�����c(di��n)�� ��̖�l�ʣ� ���l��̖��Ҫ��С�IJ�־��g�࣬�ԜpС����Ч��(y��ng)�������̖�����ԡ� ���g�g�ࣺ ��������Խ����PCB�ӣ��_�����g�g������ԜpС��?d��ng)_�� �迹ƥ�䣺 ��־��Č��Ⱥ��g����Ӱ����迹��ʹ��PCB�O(sh��)Ӌ(j��)���߿����M(j��n)���迹ƥ���Ӌ(j��)�㡣 ��������ԣ� �_���x��IJ�־��g�����PCB�����̵�������ˇҪ�� EMCҪ�� ����������늴ż�����Ҫ����Ҫ����(j��)�O(sh��)Ӌ(j��)��(bi��o)��(zh��n)��Ҏ(gu��)�����x���־����g�ࡣ ���M(j��n)�в�־����֕r�����ʹ�Ì��I(y��)��PCB�O(sh��)Ӌ(j��)���ߣ��@�ӿ��Ը��õ��M(j��n)���迹ƥ�䡢��̖�����Է����Լ��M���ض����O(sh��)Ӌ(j��)Ҫ���⣬�cPCB�����̜�ͨ���˽������������ͽ��hҲ�Ƿdz���Ҫ�ġ� |

| ��PCB��S����ľ����a(b��)�������қ]�����e����(y��ng)ԓ�Ǟ��˴_���g�̾�·��ij�Ʒ�����_(d��)��Ҫ�����Ҫ��һ�����a(b��)�����@���a(b��)��һ�㲻��̫�࣬��Ҫ�����־��Л]�о����ć�(y��n)��Ҫ���ˡ���������e��(y��n)���Ҫ���a(b��)�����}Ҳ����t�������Ҫ���]���������{(di��o)���g���ˡ���Ҫ���㌍(sh��)�H����Ҫ������Ը������_�J(r��n)���a(b��)�����پ�֪��������ŕ��g�̵����پ����ˡ� |

С����|51�����Փ��

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664

Powered by ��Ƭ�C(j��)�̳̾W(w��ng)