|

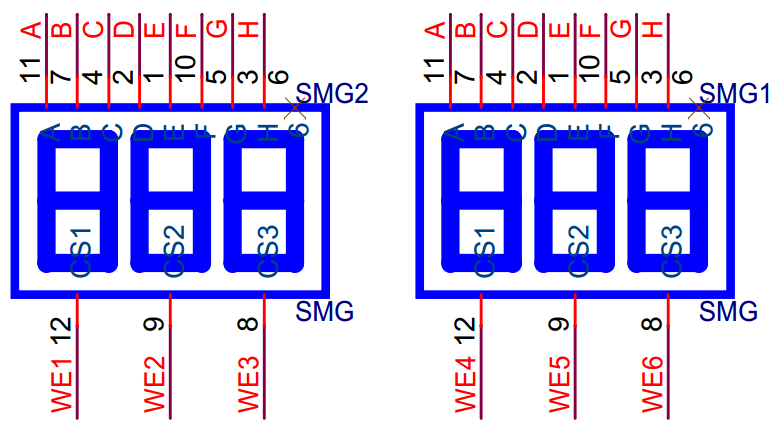

| U5選擇哪個數(shù)碼管,U4給這個數(shù)碼管送值 |

| U5段選,U4位選。 |

|

74HC595是一個串入、并出的IO轉換芯片,也可以級聯(lián),級聯(lián)時Q7同時為輸出端。 74HC595有三態(tài)輸出功能。 移位寄存器和存儲器有各自的時鐘。 sTcp端是存儲寄存器的時鐘輸入 sHcp端是移位寄存器的時鐘輸入 OE(非)輸出使能 MR(非) 芯片復位 DS 串行數(shù)據(jù)輸入端 |

| 段選,位選,如果想同時顯示,需考慮刷新頻率問題。595的原理自己找個PDF看看就懂了,很簡單 |

| U4段選,U5位選,如果想要實現(xiàn)6位同時顯示,需要考慮刷新頻率,已肉眼觀察不閃爍為準。 |

|

74HC595是一個8位串行輸入、并行輸出的位移緩存器; 具體這個,沒說錯的話:U5是位選,U4是段選,想顯示某一位,需要兩字節(jié)數(shù)據(jù)串并轉換,一字節(jié)位選,一字節(jié)位選,延時幾mS,在顯示下一位 |

| 74HC595是一個8位串行輸入、并行輸出的位移緩存器:并行輸出為三態(tài)輸出。在SCK 的上升沿,串行數(shù)據(jù)由SDL輸入到內(nèi)部的8位位移緩存器,并由Q7'輸出,而并行輸出則是在LCK的上升沿將在8位位移緩存器的數(shù)據(jù)存入到8位并行輸出緩存器。當串行數(shù)據(jù)輸入端OE的控制信號為低使能時,并行輸出端的輸出值等于并行輸出緩存器所存儲的值。而當OE為高電位,也就是輸出關閉時,并行輸出端會維持在高阻抗狀態(tài)。 |

| 參與人數(shù) 2 | 黑幣 +18 | 收起 理由 |

|---|---|---|

|

| + 8 | |

|

| + 10 | 回帖助人的獎勵! |

| U4段選,U5位選。 |

Powered by 單片機教程網(wǎng)