��(bi��o)�}: CPLD�ನ����̖�l(f��)���� [��ӡ���]

����: 51��ss �r(sh��)�g: 2016-3-30 21:17

��(bi��o)�}: CPLD�ನ����̖�l(f��)����

ժ Ҫ

ֱ�Ӕ�(sh��)���l�ʺϳ�(Direct Digital Synthesis��DDS)��20���o(j��)60���ĩ���F(xi��n)�ĵ������l�ʺϳɼ��g(sh��)��ԓ���g(sh��)����λ������l(f��)���ԕr(sh��)��ɘӶ������A(ch��)���ڕr(sh��)�����M(j��n)���l�ʺϳɣ����Կɾ���߉����(CPLD)������Ƽ���(sh��)��(j��)̎���ĺ��ģ��Ɍ����Δ�(sh��)��(j��)��D/A�D(zhu��n)�Q�����ٻ֏�(f��)������CPLD��DDS���g(sh��)�ĺ���(sh��)�l(f��)�������Ԍ�(sh��)�F(xi��n)��̖���εĶ��ӻ���ͬ�r(sh��)������ݔ����̖�Ď�����

����(g��)�O(sh��)Ӌ(j��)����MAX+ plus II�_�l(f��)ƽ�_��VHDL���̌�(sh��)�F(xi��n)�����ڿɾ���߉����CPLD�O(sh��)Ӌ(j��)�ನ����̖�l(f��)��������VHDL���̌�(sh��)�F(xi��n)�����O(sh��)Ӌ(j��)�^�̺��Σ��O���ģ�����ֲ�ԏ�(qi��ng)��ϵ�y(t��ng)��CPLD����ģ�����ֱ�Ӕ�(sh��)�ֺϳɼ��g(sh��)���o�Ա�Ҫ��ģ�M�·����(g��u)��һ��(g��)���η�(w��n)���������^�ߵĺ���(sh��)��̖�l(f��)������ϵ�y(t��ng)����ɫ���ڳ����w��ʎ����A/D�D(zhu��n)�Q�⣬ȫ��������һƬCPLDоƬ�ϣ�ʹϵ�y(t��ng)���������ݔ���l�ʡ����ȿ��{(di��o)�����Ҳ������Dz�����������������CPLD���пɾ����������ԣ�������Է���ظ��Q���Δ�(sh��)��(j��)���Һ������У�����O�㡣

�P(gu��n)�I�~����̖�l(f��)�����O(sh��)Ӌ(j��)�����ࣻVHDL��CPLD��MAX+ plus II

ABSTRACT

Direct digital frequency synthesize(DDFS) is a recently and rapidly developed technology which features high frequency resolution��This paper briefly introduces the basic principle of DDS. The basic principle and performance of CPLD chip��Then it mainly describes how to use CPLD chip to design a function generator of high accuracy��The principle of three-phase multi-signal generator based on CPLD and DDS technology is introduced��Based on these��the modules of CPLD design are given��

The multi-wave signal generator is designed based on program-mable logical component CPLD��The VHDL programming realization and the MAX+ plus II development platform. Besides the crystal oscillator and the A/D transformation��the entire system completely integrates on the CPLD chip��The multi-wave signal generator may output the sine-wave��the triangle-wave��the square-wave��Then downloaded under the situation which the entire system hardware connects do not change��and finally output the special profile which user needs��The multi-wave signal generator generates wave which the conventional function signal generators can��t make��Moreover because of the programmable reset feature of the CPLD��the generator can change the wave data conveniently and practice easily��The whole design realizes by the VHDL programmer��Its design process has simple feature��easy modification and high transportation��

Keywords��Signal Generator Design��Three-phase��VHDL��CPLD��MAX+ plus II

Ŀ �

1 �� �� 1

2����CPLD������ನ�κ���(sh��)�l(f��)�����O(sh��)Ӌ(j��) 3

2.1 ���ΰl(f��)����ϵ�y(t��ng)���O(sh��)Ӌ(j��)�������似�g(sh��)ָ��(bi��o) 3

2.1.1�O(sh��)Ӌ(j��)��ʽ���� 3

2.1.2 ���ຯ��(sh��)�ನ�ΰl(f��)�������g(sh��)ָ��(bi��o) 5

2.1.3���ನ�ΰl(f��)�����O(sh��)Ӌ(j��)�������� 5

2.2 �O(sh��)Ӌ(j��)���� 6

2.2.1 ���ຯ��(sh��)�l(f��)�����O(sh��)Ӌ(j��)ԭ�� 6

2.2.2 �ನ�ΰl(f��)�����ĸ���(g��)����ģ�K�O(sh��)Ӌ(j��)��ʽ���� 9

2.3 �{(di��o)ԇ���� 12

2.3.1 CPLD��ʹ���������Ć��} 12

2.3.2 �����·���{(di��o)ԇ 13

2.3.3 DAC�·���{(di��o)ԇ 13

2.3.4 ������{(di��o)ԇ 13

2.3.5 Ӳ���·���{(di��o)ԇ 13

�Y(ji��) Փ 15

�����īI(xi��n) 16

���1 ����ನ�κ���(sh��)�l(f��)������ģ�K�ij��� 17

���2 Ԫ����B 23

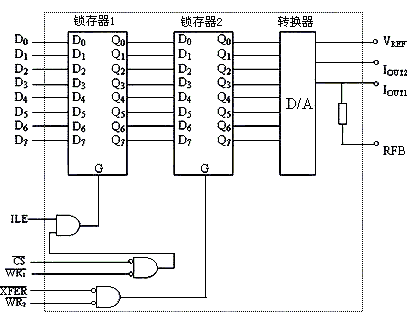

1 DAC0832 23

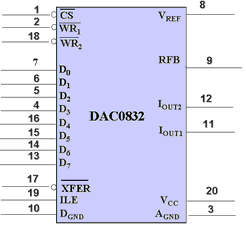

2 LM324 24

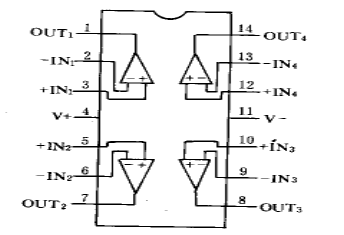

3 PM7128SLC84-15оƬ 25

���3�·ԭ��D 26

���4 Ӣ���Y�ϼ��g�� 27

1Ӣ���Y�� 27

2Ӣ���g�� 36

�� �x 43

1 �� ��

�F(xi��n)����Ӽ��g(sh��)�ĺ��ļ��g(sh��)��EDA��Electronic Design Automation����EDA���g(sh��)������ه��(qi��ng)������Ӌ(j��)��C(j��)��EDA�_�l(f��)ƽ�_�ϣ���Ӳ�������Z��HDL(Hardware Description Language)ϵ�y(t��ng)߉�����ֶ���ɵ��O(sh��)Ӌ(j��)�ļ����Ԅӵ����߉���g��߉������߉�ָ߉�C�ϡ��Y(ji��)��(g��u)�C�ϣ����ֲ��������Լ�߉��(y��u)���ͷ���yԇ��ֱ����(sh��)�F(xi��n)�ȶ�����Ӿ�·ϵ�y(t��ng)���ܡ�EDA���g(sh��)ʹ���O(sh��)Ӌ(j��)�ߵĹ����H��������ܛ���ķ�ʽ��������Ӳ�������Z�Ժ�EDAܛ������Ɍ�ϵ�y(t��ng)Ӳ�����ܵČ�(sh��)�F(xi��n)��

EDAʹ����Ӽ��g(sh��)�I(l��ng)����W(xu��)�ƵĽ�����ģ���������o(h��)����ݣ�ģ�M�c��(sh��)�֡�ܛ���cӲ����ϵ�y(t��ng)�c�������О��c�Y(ji��)��(g��u)��ASIC��Application Specific Integrated Circuit,���ü����·���cFPGA��Field Programmable Gate Array���ȡ�

EDA���g(sh��)��21���o(j��)�õ��ĺܴ��M(j��n)�����������Ҏ(gu��)ģ��FPGA��CPLD��Complex Programmable Logic Device�������IJ����Ƴ���ܛӲ��IP��(Intellectual Property)������ИI(y��)�Įa(ch��n)�I(y��)�I(l��ng)���g(sh��)�I(l��ng)����O(sh��)Ӌ(j��)��(y��ng)���I(l��ng)��õ��M(j��n)һ���Ĵ_�J(r��n)��ϵ�y(t��ng)�����О��(y��n)�C��Ӳ�������Z��(System C)�ij��F(xi��n)��ʹ��(f��)�s���ϵ�y(t��ng)���(y��n)�Cڅ�ں��Ρ�

Ӳ�������Z��VHDL[ȫ����VHSIC(Very High Speed Integrated Circuit) Hardware Description Language]��EDA���g(sh��)����Ҫ�M�ɲ���,�������������l(f��)����(chu��ng)������IEEE (The Institute of Electrical and Electronics Engineers)�M(j��n)һ���l(f��)չ���l(f��)������Ӳ�������Z�ԵĘI(y��)���(bi��o)��(zh��n)֮һ��

VHDL�Z�Ծ��к�(qi��ng)���·�����ͽ�ģ�������Ķ���(g��)�ӴΌ���(sh��)��ϵ�y(t��ng)�M(j��n)�н�ģ���������Ķ������Ӳ���O(sh��)Ӌ(j��)�΄�(w��)��������O(sh��)Ӌ(j��)Ч�ʺͿɿ��ԡ�

VHDL�����c���wӲ���·�o�P(gu��n)���c�O(sh��)Ӌ(j��)ƽ�_�o�P(gu��n)�����ԣ����Ҿ������õ��·�О�������ϵ�y(t��ng)������������VHDL֧�ָ��Nģʽ���O(sh��)Ӌ(j��)��������������c������ϻ��Ϸ��������挦��(d��ng)����Ӯa(ch��n)Ʒ�������ڿs�̣���Ҫ��������O(sh��)Ӌ(j��)���������¼��g(sh��)����׃��ˇ�ȷ��棬VHDL�������õ��m��(y��ng)�ԡ�

�����������̻��m����(x��)�T�Ͻ������d���@Ҫͨ�^���dܛ��ƽ�_�������d��|��(sh��)�F(xi��n)���@���O(sh��)Ӌ(j��)�^���е���Ҫ���E����������MAX+PLUS��ܛ����Ӌ(j��)��C(j��)������O(sh��)Ӌ(j��)�����d��Ŀ��(bi��o)�����С�EDA����ܛ�����¿��Է֞�5��(g��)ģ�K���O(sh��)Ӌ(j��)ݔ�뾎������������HDL�C�������m���������d���ȡ�

Direct Digital Synthesis(DDS)��20���o(j��)60���ĩ���F(xi��n)�ĵ������l�ʺϳɼ��g(sh��)��ԓ���g(sh��)����λ������l(f��)���ԕr(sh��)��ɘӶ������A(ch��)���ڕr(sh��)�����M(j��n)���l�ʺϳɣ����Կɾ���߉����(CPLD)������Ƽ���(sh��)��(j��)̎���ĺ��ģ�������Flash ROM�IJ��Δ�(sh��)��(j��)��D/A�D(zhu��n)�Q�����ٻ֏�(f��)��DDS�l���D(zhu��n)�Q�ٶȿ죬�l�ʷֱ��ʸߣ������l���D(zhu��n)�Q�r(sh��)�ɱ�����λ���B�m(x��)��������ڌ�(sh��)�F(xi��n)��N�{(di��o)�ƹ��ܡ�DDS��ȫ��(sh��)�ֻ����g(sh��)������ȡ���λ���l�ʾ��Ɍ�(sh��)�F(xi��n)�̿أ�����ͨ�^���Q���Δ�(sh��)��(j��)�`�(sh��)�F(xi��n)���Ⲩ�Ρ����⣬DDS���چ�Ƭ���ɣ��w�eС���r(ji��)��ͣ�����С�����DDS���g(sh��)������õ����w�ٰl(f��)չ���䑪(y��ng)��ҲԽ��Խ�V��������CPLD��DDS���g(sh��)�ĺ���(sh��)�l(f��)�������Ԍ�(sh��)�F(xi��n)��̖���εĶ��ӻ������ҷ���ɿ������ν�(j��ng)��(j��)��ϵ�y(t��ng)���ڔU(ku��)չ��ͬ�r(sh��)�ɴ�����ݔ����̖�Ď�����

CPLD���B�m(x��)ʽ���B�Y(ji��)��(g��u)���������_����(n��i)��߉��Ԫ���Լ���߉��Ԫ֮�g����ͨ�^ȫ�ֻ��B�����еĶ�·�x���������xͨ��(g��u)����̖ͨ·������Ҫ���c(di��n)�ǃ�(n��i)���r(sh��)�g�ӕr(sh��)�c����߉�Y(ji��)��(g��u)�ȟo�P(gu��n)����ģ�K֮�g�ṩ�˾��й̶��r(sh��)�ӵĿ��ٻ��Bͨ������˿����A(y��)�y�r(sh��)�g�ӕr(sh��)��������������ð�U(xi��n)�ȬF(xi��n)���ڸ��N߉�·�O(sh��)Ӌ(j��)��

���ĵ�DDSϵ�y(t��ng)��CPLD����ģ�����ֱ�Ӕ�(sh��)�ֺϳɼ��g(sh��)���o�Ա�Ҫ��ģ�M�·����(g��u)��һ��(g��)���η�(w��n)���������^�ߵĺ���(sh��)��̖�l(f��)��������ϵ�y(t��ng)����ɫ����CPLD�м����˴��·��ʹϵ�y(t��ng)�������ݔ����������Ҳ������������Dz���߀���M(j��n)�в��δ惦,���N����֮�g����λ�����120�㣬�������CPLDϵ�y(t��ng)��

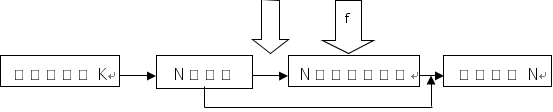

DDS����Փ����(j��)���ο�˹�س�Ӷ���������(j��)ԓ����������һ��(g��)�������Ҳ��B�m(x��)��̖������������λ�S�����Ե�������λ�g�����M(j��n)����λ/���ȳ�ӣ��õ�һ��(g��)�����Ե�������̖���xɢ��λ�ķ������У����Ҍ�ģ�M�����M(j��n)��������������ķ�ֵ��������(y��ng)�Ķ��M(j��n)�Ɣ�(sh��)��(j��)���a���@�ӾͰ�һ��(g��)���ڵ����Ҳ��B�m(x��)��̖�D(zhu��n)�Q�ɞ�һϵ���xɢ�Ķ��M(j��n)�Ɣ�(sh��)������Ȼ��ͨ�^һ�����ֶι̻���ֻ�x�惦��ROM �У�ÿ��(g��)�惦��Ԫ�ĵ�ַ������λȡ�ӵ�ַ���惦��Ԫ�ă�(n��i)�����ѽ�(j��ng)�����˵����Ҳ���ֵ���@�ӵ�һ��(g��)ֻ�x�惦���͘�(g��u)����һ��(g��)�c2�����ڃ�(n��i)��λȡ��������(y��ng)�����Һ���(sh��)���������惦����һ��(g��)���ڵ����Ҳ����η�ֵ������ַQ������Ҳ��δ惦�����˕r(sh��)�����Ҳ�����̖����λ�c�r(sh��)�g�ɾ����P(gu��n)ϵ������(j��)�@һ�����P(gu��n)ϵ����һ���l�ʵĕr(sh��)���̖�����£�ͨ�^һ��(g��)���Ե�Ӌ(j��)��(sh��)�r(sh��)��l(f��)�������a(ch��n)����ȡ�ӵ�ַ���ѵõ������Ҳ����δ惦���M(j��n)�В��裬�M(j��n)�������Ե��xȡ���δ惦���еĔ�(sh��)��(j��)����ݔ��ͨ�^��(sh��)ģ�D(zhu��n)�Q������ͨ�V�����Ϳ��Ժϳ�һ��(g��)�����ġ�����һ���l�ʵ����Ҳ���̖��DDS�·һ�����ϵ�y(t��ng)�r(sh��)犡���λ�ۼ�������λ�{(di��o)������ROM ���ұ���D/A�D(zhu��n)�Q���͵�ͨ�V����(LPF)��

����CPLD��DDS���g(sh��)�ĺ���(sh��)�l(f��)�������Ԍ�(sh��)�F(xi��n)��̖���εĶ��ӻ������ҷ���ɿ������ν�(j��ng)��(j��)��ϵ�y(t��ng)���ڔU(ku��)չ��ͬ�r(sh��)�ɴ�����ݔ����̖�Ď�����

2����CPLD������ನ�κ���(sh��)�l(f��)�����O(sh��)Ӌ(j��)

2.1 ���ΰl(f��)����ϵ�y(t��ng)���O(sh��)Ӌ(j��)�������似�g(sh��)ָ��(bi��o)

2.1.1�O(sh��)Ӌ(j��)��ʽ����

����ӹ����O(sh��)Ӌ(j��)�c�yԇ�У�������ҪһЩ��������Ҫ�����̖��Ҫ���䲨�ήa(ch��n)���࣬�l�ʷ�����{(di��o)��ͨ������̖�a(ch��n)�����y�ԝM��Ҫ���Ј��ϳ��۵�������̖�a(ch��n)�����r(ji��)���F�����ώ�ָ��(d��o)�£��Y(ji��)�ό�(sh��)�HҪ�����O(sh��)Ӌ(j��)��һ�N����CPLD������ನ�κ���(sh��)�l(f��)��������ݔ�����Ҳ������Dz��������Ȳ�����̖��������̖֮�g����λ�����120˚��

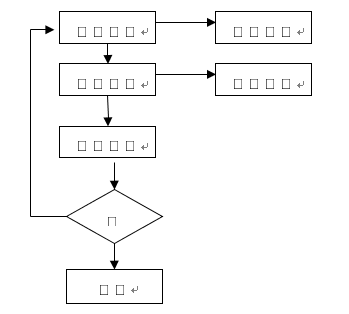

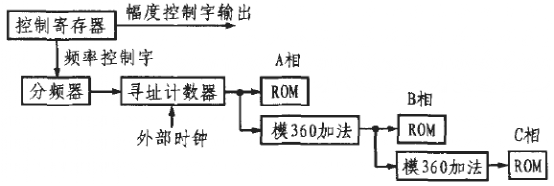

��(f��)�s�ɾ���߉����CPLD�������Դ����S�����Ԫ�������Ķ�������·��ď�(f��)�s�̶ȡ�����CPLD�������O(sh��)Ӌ(j��)һ����Է֞��O(sh��)Ӌ(j��)ݔ�롢�O(sh��)Ӌ(j��)��(sh��)�F(xi��n)��������������(g��)�O(sh��)Ӌ(j��)���E�Լ�����(y��ng)�Ĺ��ܷ��桢�r(sh��)�����������yԇ����(g��)�O(sh��)Ӌ(j��)�(y��n)�C�^�̡�

�O(sh��)Ӌ(j��)ݔ���ж�N��ʽ��Ŀǰ��õ����·�D��Ӳ�������Z�ԃɷN�����ں��ε��O(sh��)Ӌ(j��)���ɲ���ԭ��D�ķ�ʽ�O(sh��)Ӌ(j��)�����ڏ�(f��)�s���O(sh��)Ӌ(j��)��ʹ��ԭ��D��Ӳ�������Z��(Verilog, AHDL, VHDL�Z��)�����߃����ã����ÌӴλ��O(sh��)Ӌ(j��)��������ģ�K�Ӵε��M(j��n)��������

ԭ��D�O(sh��)Ӌ(j��)������Ҫ�ǰ��Ք�(sh��)��ϵ�y(t��ng)�Ĺ��ܲ��þ��w��߉�����M�ρ팍(sh��)�F(xi��n)�İ��@Щ�ɾ��w������(sh��)�F(xi��n)߉���ܵ��·�Dݔ�뵽ܛ����(d��ng)�С��@�N�O(sh��)Ӌ(j��)�������^ֱ�^��

Ӳ�������Z���O(sh��)Ӌ(j��)������Ҫ�є�(sh��)��ϵ�y(t��ng)��߉������Ӳ���Z�ԁ�����������VHDL�Z�������Ĕ�(sh��)��ϵ�y(t��ng)���������N����һ�Q���О����������Îׂ�(g��)��������������Z����M(j��n)������ݔ���cݔ��֮�g���D(zhu��n)�Q�P(gu��n)ϵ������ǔ�(sh��)��(j��)����������һϵ�еIJ��l(f��)��̖�xֵ�Z������ݔ���cݔ��֮�g���P(gu��n)ϵ��������Y(ji��)��(g��u)������ʽ����ͨ�^Ԫ��֮�g�Ļ�(li��n)�P(gu��n)ϵ����ݔ���·�ĽY(ji��)��(g��u)���oՓ��ԭ��Dݔ��߀�������Z��ݔ�붼�����䃞(y��u)�c(di��n)��ԭ��D�O(sh��)Ӌ(j��)�m���ڌ��������^��Ϥ��Ԫ��֮�g�Ļ�(li��n)�����������Ҫ���O(sh��)Ӌ(j��)���^���ε���r����������������Ϥ���O(sh��)Ӌ(j��)��(f��)�s����r���f��ʹ��Ӳ�������Z��Ҫ����һЩ��

�O(sh��)Ӌ(j��)��(sh��)�F(xi��n):�O(sh��)Ӌ(j��)��(sh��)�F(xi��n)��ָ���O(sh��)Ӌ(j��)ݔ���ļ����۽z�D�ļ�(CPLD)�ľ��g�^�̡���ԓ�^���У����gܛ���Ԅӵ،��O(sh��)Ӌ(j��)�ļ��M(j��n)�оC�ϡ���(y��u)������ᘌ����x�е������M(j��n)��ӳ�䡢���֡��������a(ch��n)������(y��ng)���۽z�D��λ����(sh��)��(j��)�ļ����ڴ��^���У����ھ��gܛ���oϵ�y(t��ng)���_�ķ����DZ��^�s�y�ģ������·�岼���ķ��㣬�Ñ����Ԍ�ݔ��/ݔ�����_�M(j��n)�й��_�i����

��������:�������̾��nj��۽z�D�ļ���λ����(sh��)��(j��)�ļ����d������(y��ng)��CPLD�����У����cCPLD�����Ĺ��_������(y��ng)�����õ�ܛ����ALTARE��˾�ṩ��CPLDDN4���@��ALTARE��˾CPLDϵ�еČ������dܛ����

�O(sh��)Ӌ(j��)У�(y��n):����(y��ng)���O(sh��)Ӌ(j��)ݔ�롢�O(sh��)Ӌ(j��)��(sh��)�F(xi��n)���������̣��O(sh��)Ӌ(j��)�(y��n)�C�֞��˹��ܷ��桢�r(sh��)����桢�����yԇ����(g��)���֡����ܷ����(y��n)�C�O(sh��)Ӌ(j��)��߉���ܣ����O(sh��)Ӌ(j��)ݔ���^���У������ֹ��ܻ�����(g��)�O(sh��)Ӌ(j��)�����M(j��n)�з��棻�r(sh��)����������O(sh��)Ӌ(j��)��(sh��)�F(xi��n)�Ժ�ᘌ������IJ��֡����������M(j��n)�Еr(sh��)�ӷ��棬�������r(sh��)�P(gu��n)ϵ:�����yԇ�����������̺�ͨ�^��(sh��)�(y��n)������yԇ���ߣ��yԇ������K�Ĺ��ܺ�����ָ��(bi��o)��

���O(sh��)Ӌ(j��)��ϵ�y(t��ng)�Ľӿ��·����̖Դ�Ĵ����(sh��)߉���ƶ���CPLD�Ќ�(sh��)�F(xi��n)��

��ԓ�����з��������c(di��n)�������ֿɷ֞鹦�ܷ���(ǰ����)�c�r(sh��)�����(�����)������(j��)�·�O(sh��)Ӌ(j��)���Ʒ����ļ������ļ����C��ǰ�M(j��n)�з��棬���(y��n)�C�·���ܣ��ڱ��C�·�ь�(sh��)�F(xi��n)�O(sh��)Ӌ(j��)�Ĺ��ܺ��M(j��n)�оC�ϲ����C�ϵĽY(ji��)���M(j��n)�Еr(sh��)����棬���(y��n)�C�·�ĕr(sh��)���Ƿ�M��Ҫ��(d��ng)�·��ǰ�����c����涼�M��Ҫ�t�·���O(sh��)Ӌ(j��)�dzɹ��ġ�Ȼ���O(sh��)��������Ͳ��M(j��n)�����_�i�����ٌ��ļ��M(j��n)���m�����������õ�߉�C�ϣ�ͨ�^������O(sh��)Ӌ(j��)�����Y(ji��)��ϵ�y(t��ng)�е����������M(j��n)���B�{(di��o)����l(f��)�F(xi��n)���}�����O(sh��)Ӌ(j��)��

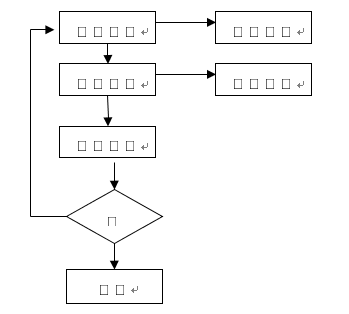

���O(sh��)Ӌ(j��)��ʹ����ALTERA��˾�ṩ������ܛ��MAX+PLUSII�M(j��n)���ļ���ݔ�롢���g�����d��MAX+PLUSII��ܛ���O(sh��)Ӌ(j��)��Ҫ���O(sh��)Ӌ(j��)ݔ�롢�(xi��ng)Ŀ���g���(xi��ng)ĿУ�(y��n)���������̵��IJ��֘�(g��u)�ɡ�

�D2.1-1 CPLD�O(sh��)Ӌ(j��)���̈D

�D2.1-2 MUS+PLUS���O(sh��)Ӌ(j��)����Ҫ�M�ɲ���

2.1.2 ���ຯ��(sh��)�ನ�ΰl(f��)�������g(sh��)ָ��(bi��o)

���N����֮�g����λ�����120�㣬����ͬ�r(sh��)ݔ������������Ĺ��ܡ����������N���ε��l�ʾ�Ҫ�a(ch��n)�����l�ʶ������A(y��)�ã�ݔ������̖��ֵ����100mv~3V�ķ�����(n��i)�{(di��o)����

�����Ҳ���̖��Ҫ��飺��̖�l�ʷ�����20Hz-20kHz֮�g���{(di��o)�����L��10Hz��

�Ǿ���ʧ��ϵ��(sh��)��3%��

��������̖��Ҫ���ǣ���̖�l�ʷ�����20Hz-20kHz���������½��r(sh��)�g<1��s��

�����Dz���̖��Ҫ��飺��̖�l�ʷ�����20Hz-20kHz֮�g���{(di��o)��

2.1.3���ನ�ΰl(f��)�����O(sh��)Ӌ(j��)��������

Direct Digital Synthesis(DDS)��20���o(j��)60���ĩ���F(xi��n)�ĵ������l�ʺϳɼ��g(sh��)����DDS���g(sh��)���O(sh��)Ӌ(j��)����һ��(g��)����CPLD������ನ�κ���(sh��)�l(f��)��������ʹ����ݔ�����Ҳ������Dz��������Ȳ�����̖Դ�����N���ε���λ���120˚��

���ΰl(f��)�����е�CPLDоƬ��DDS�Ŀ��Ƽ���(sh��)��(j��)̎���ĺ��ģ��·ϵ�y(t��ng)��Ҫ�ɕr(sh��)���̖�l(f��)���������Δ�(sh��)��(j��)�a(ch��n)������A/D�D(zhu��n)�Q�·�M�ɡ����Δ�(sh��)��(j��)�a(ch��n)�����ɔ�(sh��)�ط��l�������Dz��a(ch��n)��ģ�K�����Ҳ��a(ch��n)��ģ�K�������a(ch��n)��ģ�K�Ș�(g��u)�ɡ��ڕr(sh��)���̖�l(f��)���������£����Δ�(sh��)��(j��)�a(ch��n)���������l�ʿ�׃�IJ��Δ�(sh��)��(j��)��(sh��)����̖���� A/D�D(zhu��n)�Q�·�Ŵ�̎����ݔ����K����Ҫ�IJ�����̖��

����(g��)ģ�K�Č�(sh��)�F(xi��n)��Ҫ����MAX+ plus II�_�l(f��)ƽ�_����VHDL���̌�(sh��)�F(xi��n)�����������·�ĺ���֮����CPLD�Č������dܛ���Ѿ�����ij�������CPLDоƬ���ٌ�����(g��)���ΰl(f��)�����M(j��n)���{(di��o)ԇ��ʹ���_(d��)���A(y��)�ڵ�Ч����

2.2 �O(sh��)Ӌ(j��)����

2.2.1 ���ຯ��(sh��)�l(f��)�����O(sh��)Ӌ(j��)ԭ��

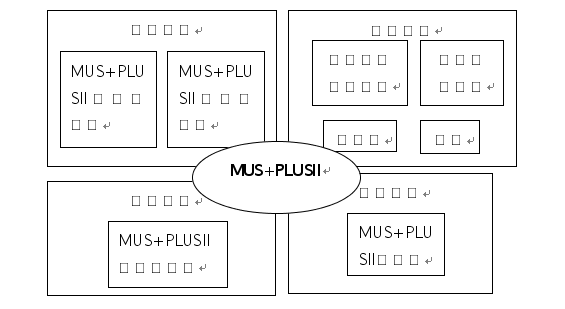

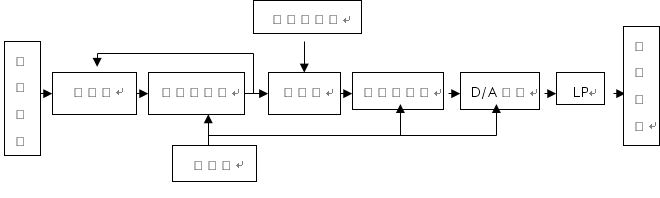

DDS���������ನ�ΰl(f��)������Ҫ�ɘ�(bi��o)��(zh��n)�����l��Դ����λ�ۼ��������δ惦������(sh��)ģ�D(zhu��n)�Q������ͨƽ���V������(g��u)�ɡ��ڕr(sh��)��}�_�Ŀ����£��l�ʿ�����K����λ�ۼ����õ�����(y��ng)����a����a��ַ���δ惦���M(j��n)����a�������a׃�Qݔ����ͬ�ķ��Ⱦ��a���ٽ�(j��ng)�^��(sh��)ģ׃�Q���õ�����(y��ng)���A�ݲ������(j��ng)��ͨ�V�������A�ݲ��M(j��n)��ƽ�������õ����l�ʿ����֛Q�����B�m(x��)׃����ݔ�����Ρ����У������l��Դһ����һ��(g��)�߷�(w��n)���ľ��w��ʎ������ݔ����̖����DDS�и�����ͬ����������ˣ�DDSݔ���ĺϳ���̖���l�ʷ�(w��n)�����c���w��ʎ����һ�ӵġ�

DDSϵ�y(t��ng)������Nλ��λ�ۼ�������λ�ۼ����ĽY(ji��)��(g��u)һ��Nλ���L�Ķ��M(j��n)�Ƽӷ����cһ��(g��)�ɕr(sh��)��|�l(f��)��Nλ���M(j��n)����λ�ۼӼĴ�����(li��n)��(g��u)�ɣ��ӷ�����һ��(g��)ݔ����c��λ�Ĵ�����ݔ�������B����һ��(g��)ݔ������ⲿ���l�ʿ�����K����ÿһ��(g��)�����r(sh��)��}�_ݔ��r(sh��)�����l�����ۼ�һ�Σ�������Ӻ�ĽY(ji��)�������ۼӼĴ����Ĕ�(sh��)��(j��)ݔ���ˡ�������λ�ۼ�����ݔ���B���ڲ��δ惦���ĵ�ַ���ϡ������ݔ���ĸ�׃���ஔ(d��ng)���M(j��n)�в����ϵ�y(t��ng)�еą����r(sh��)�ͨ����һ��(g��)�߷�(w��n)���Եľ��w��������Á�����ϵ�y(t��ng)�r(sh��)�ͬ������(g��)ϵ�y(t��ng)�ĸ��M�ɲ��֡���ϵ�y(t��ng)�r(sh��)��}�_�������£���λ�ۼ�����ͣ���ۼӣ�Ҳ����ͣ�ز������ͣ�ذѲ������ºϳɳ�������(d��ng)��λ�ۼ����ۼӝM�r(sh��)�͕��a(ch��n)��һ����������һ��(g��)�����ԵĄ������@��(g��)���ھ���DDS�ϳ���̖��һ��(g��)�l�����ڣ��ۼ���������l�ʾ���DDSݔ������̖�l�ʡ����V�����t�M(j��n)һ��ƽ��D/A�D(zhu��n)�Q��ݔ���Ľ������貨�ε���X�A�ݲ���ͬ�r(sh��)�V������Ҫ���s����

�D2.2-1 DDS��ԭ��D

�D2.2-2 ��λ�ۼ����ĽY(ji��)��(g��u)ʾ��D

���l�ʿ������O(sh��)��M����λ�ۼ�����Nλ�������r(sh��)��l��f�㣬�tݔ���l�ʞ�Mf��/2a(a=N)��DDS��ݔ���l�����ތ���(y��ng)���l�ʿ�����M=0�����Σ���ݔ���l�ʞ�f��=0������(j��)Nyquist�ɘӶ�����DDS��ݔ�������l�ʞ�r(sh��)��l�ʵ�һ�룬��f��=½f�㡣�����ڌ�(sh��)�Hݔ����ͨ�V�����ķ��������ԣ��Ɍ�(sh��)�F(xi��n)���l�����ޞ�-2/5fo�������l�ʞ� ��DDS��ݔ���l�ʷ�����0��2/5fc������DDS��ģ�K���Y(ji��)��(g��u)����ݔ�������ɲ��β��ұ��еĔ�(sh��)��(j��)��Q������ˣ�ֻ���׃���ұ��еĔ�(sh��)��(j��)�������Է��������DDS�a(ch��n)�������Ҳ�֮����������Σ������Ҳ������������Dz�����X�������{(di��o)�l���{(di��o)�ನ�Լ���������̖��

����֕r(sh��)��(f��)��ԭ�����֕r(sh��)��(f��)�õ�ԭ���Ǹ�·��ֻ̖ռ��ͬһ�ŵ��IJ�ͬ�r(sh��)�g�g϶�M(j��n)����̖��ݔ�����w�����·�������Ì����ұ팤ַ�ĸ��ٶȣ�ʹһ��(g��)���ұ��ڲ�ͬ�r(sh��)�g�β錤��ͬ������Ҳ��ķ�ֵ�����_(d��)���p�����ұ���ռ�õ�CPLD�YԴ��Ŀ�ġ�

�·�ľ��w��(sh��)�F(xi��n)����·����λ�ϻ���120���ĵ�ַ��(sh��)��(j��)����ݔ��ͨ�^һ��(g��)���xһ���x�������M(j��n)���x���x�����Ŀ��ƶ˽����M(j��n)�Ƶ�Ӌ(j��)��(sh��)�����磬Ӌ(j��)��(sh��)����0�r(sh��)��ݔ������A��ĵ�ַ��Ӌ(j��)��(sh��)����1�r(sh��)��ݔ������B��ĵ�ַ��Ӌ(j��)��(sh��)����2�r(sh��)��ݔ������C��ĵ�ַ�����ֻҪʹݔ��������ַ������׃�����͌�(sh��)�F(xi��n)�˲���ݔ��������ַ��(sh��)��(j��)�ڕr(sh��)�g���γ����B�m(x��)��Ҳ�͌�(sh��)�F(xi��n)�������ַ��(sh��)��(j��)�ĺϳɡ��@�ӾͿ�������һ��(g��)���ұ���õ����������ֵ�������ұ�p�ٵ�?j��ng)]�вɘӷ֕r(sh��)��(f��)�Õr(sh��)��1/3����(sh��)��(j��)�ķ��x��ͨ�^�֕r(sh��)��(f��)�ã�ʹ��ͨ�^�錤һ��(g��)���ұ��õ�����λ�ϻ�����������Ҳ��ķ�ֵ����������ݔ��������ַ�ڕr(sh��)�g�����B�m(x��)�ģ�����ROM�팤ַ�ĵ�ַֻ��һ·����ˣ��mȻ�õ����������Ҳ��ķ�ֵ�����������ǰ�ADDRESS�и���֮�g���P(gu��n)ϵ�����һ��ģ���ˣ����茦���õ��ķ�ֵ�M(j��n)�з��x�����ܵõ��������Ҳ����ɲ���ADDRESS�и����ַ����P(gu��n)ϵ��֪�����x��(sh��)��(j��)ֻҪ�ѷ֕r(sh��)��(f��)�õĺϳɲ��ַ��Ӽ��ɡ�

����(sh��)�x����λ�ۼ��������L�Q�����l�ʷֱ��ʣ��O(sh��)Ӌ(j��)��ȡN=16������CPLD��Ӳ���YԴ(��Ҫ�Ǵ惦��EAB����)���ޣ��茦��λ�ۼ���ݔ����16λ��λ�M(j��n)�н�?c��i)࣬�@��ȡ16λ��λ��ǰl(f��)0λ�M(j��n)����λ�������D(zhu��n)�Q�·����A=10��ݔ����(sh��)�ַ������ж�λ10λ(D=10)��

�D2.2-3 ���Ҳ����Δ�(sh��)��(j��)�a(ch��n)��ģ�K

�@�Ӵ_���Ļ�������(sh��)���£�

��1���r(sh��)��l�ʺ�ݔ����������(j��)��֪���ⲿ�r(sh��)�Դ���l��f��=12MHz����ô��ϵ�y(t��ng)���ݔ���l��λ2/5fo=4.8 MHz��

��2���l�ʷ�������Ҫ��ݔ������̖�l�ʷ������^�������12MHz�r(sh��)�Դ����CPLD������λ�ۼ���֮ǰ������һ��(g��)�r(sh��)犷��l�����Ɍ�(sh��)�F(xi��n)10��100��1000��10000�η��l������(j��)ݔ����̖���l�ʺ;���Ҫ���x��ͬ�ķ��l�Ȍ�50MHz�r(sh��)��l�ʽ��ͣ�����λ��λ�ۼ����Ͳ��ήa(ch��n)���·�ą����r(sh��)犡�

��λ/����׃�Q��CPLD��(sh��)�F(xi��n)��λ/����׃�Q�·���O(sh��)Ӌ(j��)��һ��(g��)�y�c(di��n)������(j��)DDSԭ��������ͬ���ε�������(sh��)��(j��)�惦�ڲ��β��ұ��У�������ɶನ�ΰl(f��)���Ĺ��ܡ�ROM �Ĺ����ڱ������x�õ�Altera��˾���a(ch��n)��CPLDоƬ�Ќ�(sh��)�F(xi��n)������ڌ�(sh��)�H�O(sh��)Ӌ(j��)�У�Ҫ��ֿ��]����(sh��)��(j��)�ă�(y��u)�����}������(j��)����ą���(sh��)�x��ȡ��λ�ۼ������LM=16����ȡǰ10λ��Чλ��ݔ���������ж�λl0λ���@��ֱ�ӌ�(sh��)�F(xi��n)���Ҳ��δ惦��Ҫ210xl0bitROM�����Ҳ��ұ����{(di��o)��Maxplux2ܛ���еġ�l(f��)pm_rom����ģ�K��(sh��)�F(xi��n)��

CPLD�����x��ALTERA��˾�ġ���EPM7128S84-15������128��(g��)���Ԫ��2500��(g��)��Ч߉�T��15ns���ٶȡ�PLCC84���b��ʽ�����Դ���_���ؾ����_��ȫ�ֿ������_��JTAG���_�⣬���ṩ��64��(g��)����I/O�_���@Щ���_�����������Þ�ݔ�롢ݔ�����p��ʽ��ԓ���������c(di��n)����:

l�� һ �N�����ܵ�CM0SE EPROM������

l�� �� ��ͨ�^JTAG�ӿڌ�(sh��)�F(xi��n)�ھ����̡�

l��(n��i) �� JTAG BST�·��

l�� �� �̺��Ԫ�|�l(f��)�����Ќ����������λ���r(sh��)犺͕r(sh��)�ʹ�ܿ��ơ�

l �� �� �õĔU(ku��)չ�˷e�(xi��ng)���䣬���S��ÿ��(g��)���Ԫ�ṩ���_(d��)32��(g��)�˷e�(xi��ng)��

EPM7128S������ͨ�^4��(g��)���_��JTAG�ӿ��M(j��n)���ھ�����(ISP)�ġ�ISP���S���١���Ч�����O(sh��)Ӌ(j��)�_�l(f��)�^�����؏�(f��)���̡�JTAG(Joint Test Action Group)�ǚW��JETAG�M�������߅������(bi��o)��(zh��n)����IEEE1149. 1��(bi��o)��(zh��n)��ԓ��(bi��o)��(zh��n)�ṩ�˰弉��оƬ���Ĝyԇ������JTAG�yԇ���܃H��һ�l�ľ����往�Ľӿڼ�����(y��ng)��ܛ��������ɣ�����JTAG�ܜyԇ�·����B����r�Լ��·������_�ԡ�JTAG�Ľӿ���̖��:

lTCK (Test Clock):���ڿ��Ơ�B(t��i)�C(j��)�����f��(sh��)��(j��)��

lTMS( Test Mode Select):�x��߅�����ģʽ�����Ơ�B(t��i)�C(j��)�yԇ������

lDI ( Test Data Input):��TCK��һ���أ����ܴ��Д�(sh��)��(j��)��

lTDO( Test Data Output)����TCK���½��أ�ݔ�����Д�(sh��)��(j��)��

�҂����õ��Dz������d��|ByteBlaster�������Ԍ�MAX7000Sϵ���M(j��n)���ھ����̡�ԓ���d��|�������ׂ�(g��)����:�cPC�C(j��)���п����B��25ᘲ��^���cPCB��������B��10ᘲ��^�Լ�25ᘵ�10ᘵ�׃�Q�·�������ڌ�(sh��)�F(xi��n)������λ������׃�Q���ұ�(ROM)�Y(ji��)��(g��u)��DDS��Ҫ�֞���λ�ۼ�������λ/�����D(zhu��n)�Q��Ԫ(��ROM)����(sh��)ģ׃�Q���Լ���ͨ�V���Ȏׂ�(g��)���֡�

��λ�ۼ�������λ/�����D(zhu��n)�Q��Ԫ��CPLD��(sh��)�F(xi��n)���ٌ�ݔ�������DAC���������ͨ�^��ͨ�V�������ɵõ����貨�Ρ�

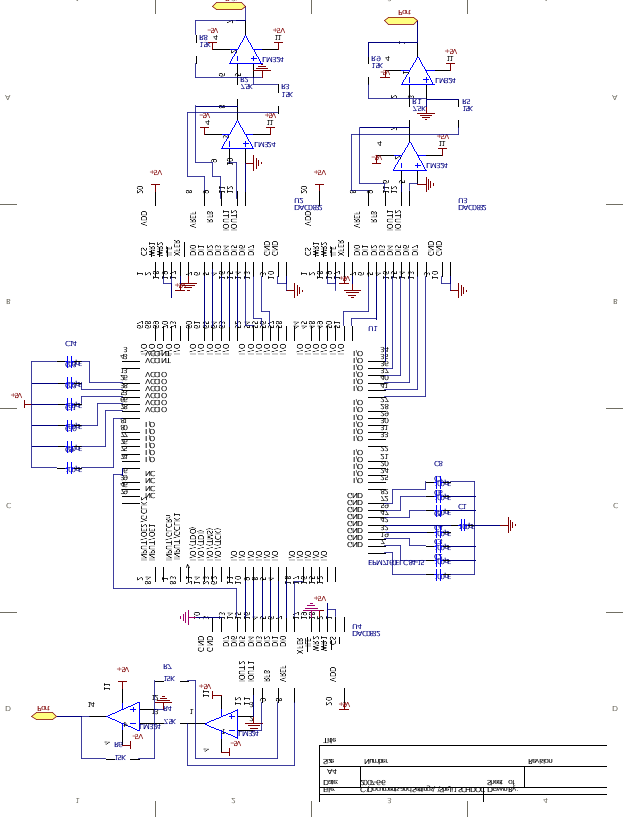

�D2.2-4 CPLD������·�B�ӈD

2.2.2 �ನ�ΰl(f��)�����ĸ���(g��)����ģ�K�O(sh��)Ӌ(j��)��ʽ����

��(sh��)�ط��l������(sh��)�ط��l���Ĺ�������ݔ���ݔ�벻ͬ��(sh��)��(j��)�r(sh��)����ݔ��r(sh��)犮a(ch��n)����ͬ�ķ��l�ȣ�ݔ����ͬ�l�ʵĕr(sh��)犣��Ը�׃ݔ����̖���l�ʡ��O(sh��)Ӌ(j��)�r(sh��)���ò����A(y��)�Ô�(sh��)�Ĝp��Ӌ(j��)��(sh��)����(sh��)�F(xi��n)�����Ĺ���ԭ���ǣ��p��Ӌ(j��)��(sh��)���ڲ����A(y��)�Ô�(sh��)�Ļ��A(ch��)�ϣ��ڕr(sh��)犵��������M(j��n)�МpӋ(j��)��(sh��)����(d��ng)Ӌ(j��)��(sh��)ֵ����r(sh��)�a(ch��n)�������̖�����d�A(y��)�Ô�(sh��)��(j��)�����Ҍ������̖������l����ݔ����̖����(sh��)�F(xi��n)���l��̖ݔ��������lϵ��(sh��)N���A(y��)�Ô�(sh��)��ֵ�����˵õ�ռ�ձȞ�50 �ľ��Εr(sh��)���̖����ݔ�����M(j��n)�ж����l���ɴˣ�ԓ���l���Ŀ����lϵ��(sh��)��2N��

���Dz����Δ�(sh��)��(j��)�a(ch��n)��ģ�K��ԓģ�K���O(sh��)Ӌ(j��)һ��(g��)����Ӌ(j��)��(sh��)����(sh��)�F(xi��n)���O(sh��)Ӌ(j��)�r(sh��)�O(sh��)��һ׃�����鹤����B(t��i)��(bi��o)־���ڴ�׃����ȫ0�r(sh��)����(d��ng)�z�y���r(sh��)犵������ؕr(sh��)�M(j��n)�м�ͬһ��(g��)��(sh��)��������ȫ1�r(sh��)���M(j��n)�Мpͬһ��(g��)��(sh��)����������A/D�D(zhu��n)�Q����8λ��DAC0832оƬ�����O(sh��)64��(g��)�r(sh��)犞�һ��(g��)���Dz����ڣ��tݔ��Qÿ�μ�8/�p8��

���Ҳ����Δ�(sh��)��(j��)�a(ch��n)��ģ�K���üӷ�Ӌ(j��)��(sh��)�����g�a�·��ɡ����Ȍ����Ȟ�1�����Ҳ���һ��(g��)���ڷ֞�64��(g��)�ɘ��c(di��n)������(j��)���Ҳ��ĺ���(sh��)�P(gu��n)ϵӋ(j��)��õ�ÿһ�c(di��n)����(y��ng)�ķ���ֵ��Ȼ��������8λ���M(j��n)�Ɣ�(sh��)��(j��)�����ֵ��255����Сֵ��0���Դ˵õ����Ҳ��������ӷ�Ӌ(j��)��(sh��)�������g�a�·��64��(g��)ݔ��ֵ���g�a�·�鲨��ݔ�����oՓ����λ�ۼ������κϳɷ�߀�ǻ���RAM��ԃ�IJ��κϳɷ��������Ա�ʾ��ϳ���̖�ķ����c�r(sh��)�g������λ���P(gu��n)ϵ����̖�ķ�������(bi��o)����ڲ��δ惦���У�ͨ�^��ַ�l(f��)�����xȡ���Δ�(sh��)��(j��)����ɔ�(sh��)�ֲ��Ρ�

�������Δ�(sh��)��(j��)�a(ch��n)��ģ�K���O(sh��)Ӌ(j��)һ��(g��)���^������(j��ng)�^��ͨ�V����������Ҳ�ͨ�^������ܮa(ch��n)��������ͨ�^�����ͳ�ȫ0��ȫ1�����o��32��(g��)�r(sh��)��ӕr(sh��)��(sh��)�F(xi��n)��64��(g��)�r(sh��)犞�һ��(g��)���ڡ�

��(sh��)��(j��)�x��������CASE�Z���O(sh��)Ӌ(j��)��ɡ���CORTROL�Ŀ������x��ݔ��һ�N���Δ�(sh��)��(j��)ݔ����ͬ�r(sh��)��ɃɷN���εľ��ԽM�ϡ����νM���nj�����ÿһ�r(sh��)�̵Ĕ�(sh��)ֵ��ӣ����˲�����DAC0832��ݔ��������������(y��ng)�ij�2������

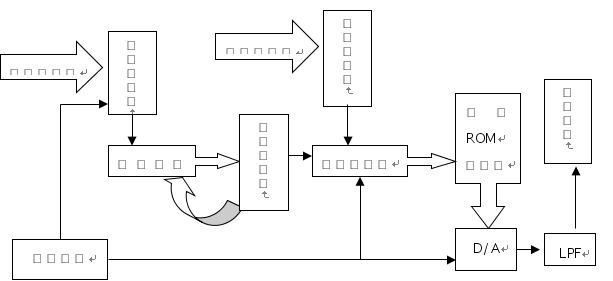

�����ɿ��ƼĴ������ⲿ����������Ĕ�(sh��)��(j��)�D(zhu��n)�Q���l�ʺͷ��ȿ����֣�Ȼ�����ɷ��l������(j��)�l�ʿ������M(j��n)�з��l����ݔ�����錤ַӋ(j��)��(sh��)���ĕr(sh��)犣���ַӋ(j��)��(sh��)���Č�ַ���g��360�ֹ�(ji��)���Ɍ�ROM�еIJ��ұ��M(j��n)�Ќ�ַ����ͨ�^ģ360�ӷ������Ԯa(ch��n)��120o����λ�

���ƼĴ������O(sh��)Ӌ(j��)�����ƼĴ����O(sh��)Ӌ(j��)��Ҫ�nj��ⲿ������ݔ��Ĕ�(sh��)��(j��)�D(zhu��n)�Q���l�ʺͷ��ȿ����֡�

���l�ȿ�׃�ķ��l��ģ�K�O(sh��)Ӌ(j��)��ԓ�O(sh��)Ӌ(j��)��Ҫ�Ǹ���(j��)�l�ʿ����֛Q�����l����(sh��)���Ķ�ݔ���c�l�ʿ�����������(y��ng)���l�ʕr(sh��)犣���ģ�K��ݔ�������錤ַӋ(j��)��(sh��)���ĕr(sh��)犡�

��ַӋ(j��)��(sh��)������Ҫ���ڮa(ch��n)����ROM��ַݔ�����Δ�(sh��)��(j��)�Č�ַ��̖����ַ���g��360�ֹ�(ji��)��

ģ360�ӷ����O(sh��)Ӌ(j��)����ģ�K�Á��a(ch��n)��120������ƣ����γ���������120���ݔ�����Ρ����ڌ�ַ���g��360�ֹ�(ji��)������ݔ����ַ��(sh��)����360�r(sh��)��회�360ȡģ��

���ұ�ROM�O(sh��)Ӌ(j��)����ģ�K��Ҫ���ڴ惦���N���Δ�(sh��)��(j��)���Ա�ͨ�^��ַӋ(j��)��(sh��)����ַݔ������(j��ng)D/ A�D(zhu��n)�Q��ݔ�����N���Σ����а������Ҳ������Dz���������

CPLD���ȿ����ֽ�(j��ng)D/A�D(zhu��n)�Qݔ����������ұ�ݔ��DAC�ą���늉���ԓ����늉���ͨ�^��׃���ȿ����ց��M(j��n)�и�׃���Ķ���׃ݔ����̖�ķ��ȡ�

�D2.2-5 CPLD�ă�(n��i)���Y(ji��)��(g��u)�O(sh��)Ӌ(j��)��D

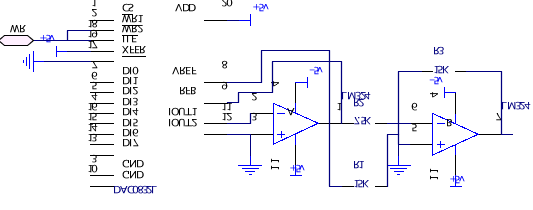

A/D�D(zhu��n)�Q������8λ��DAC0832оƬ�����εĮa(ch��n)���Dz���ֱ�Ӕ�(sh��)���l�ʺϳɼ��g(sh��)DDFS���ղ�ͬ�l��Ҫ�����l�ʿ�����n�鲽�M(j��n)����λ�����M(j��n)���ۼӣ����ۼ���λֵ�����ַ�a�xȡ�����ROM��(n��i)�IJ��Δ�(sh��)��(j��)����(j��ng)D/A�D(zhu��n)�Q�ͷ��ȿ��ƣ��ٞV�����ɵõ����Ρ�ݔ�������l���c��ַ�}�_�l�ʳ����ȣ���˸�׃�}�_�l�ʾͿ��Ը�׃ݔ�������l�ʡ�D/A�D(zhu��n)�Q�·���·�B�ӈD��Ҫ��DAC0832�� LM324��(g��u)�ɣ�������һЩ��ݺ�����������䷀(w��n)���ԣ�����ͨ�^DAC0832��̖����̖�M(j��n)�Д�(sh��)ģ�D(zhu��n)�Q���֏�(f��)��ģ�M��̖������LM324��(g��u)�ɵķŴ��·�M(j��n)�зŴ�̎����ʹ���ΰl(f��)�����_(d��)���A(y��)�ڵ�Ч����

�D2.2-6 DAC0832����B�ӈD

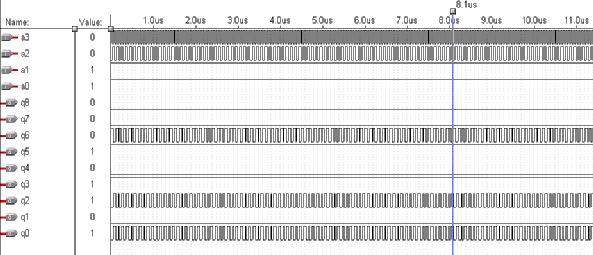

߉�r(sh��)����棺����MAX+PLUX���M(j��n)��ϵ�y(t��ng)���档�ڕr(sh��)�����У�clk��ϵ�y(t��ng)�ĕr(sh��)犣��@���O(sh��)������ĕr(sh��)犞�200ns(�����12Mhz)��freqin���l����ݔ�룬��������1-1024ȡ����ֵ���@��ȡfreqin=l(����λ�ۼ�����∆��=360˚ /1024=0.35˚)�� �tf�� = 4.88kHz��pha-seina��phaseinb��phaseinc�քe�������120˚����λ�ֵ�ݔ�룬 ȡֵ�քe�飺phaseina=0��phaseinb=341��phaseinc=683��romadddr_a��romadddr_b��ro-madddr c�քe������֕r(sh��)��(f��)���·�е�A�ࡢB���C�����λֵ(�����)��romadddr_abc��ϳ�һ·�����λֵ��

���˱�����ͬһ�����п���ͬ�r(sh��)����ݔ����(sh��)��(j��)�еĸ��(xi��ng)�������沨���M(j��n)�н�ȡ����s3��5us-8��6US�r(sh��)�ĕr(sh��)���Σ�ddsout_abc���� E�ұ����õ������ϔ�(sh��)��(j��)��ddsout_a��ddsout_b��ddsout_c�քe�锵(sh��)��(j��)���x��A�ࡢB���C�����λ����(y��ng)�ķ���ֵ�����������Ҳ�����֮�g����P(gu��n)ϵ��׃��څ�ݵ�֪��ݔ���Ĕ�(sh��)��(j��)�����_�ġ�����DDS���g(sh��)�Ǐ���λ������l(f��)������(j��)�_������λ����Ч���L�M�ϣ����a(ch��n)����λ��?c��i)��`����O(sh��)Ӌ(j��)����λ�`��Ӌ(j��)�㣺ÿ��������̖ݔ���ӕr(sh��)��2��(g��)ϵ�y(t��ng)�r(sh��)����ڣ���At=2Tc�������λ�`��飺∆��=2��*f��*∆T���t∆��=0.7˚��(�@���O(sh��)�l����M=1�����LN=10)��

����(g��)ϵ�y(t��ng)�����w��ʎ����A/D�D(zhu��n)�Q�⣬ȫ��������һƬCPLDоƬ�ϡ�����ݔ�������l�ʡ����ȿ��{(di��o)�����Ҳ������Dz������������Ⲩ��ģ�K�����Ñ����о����貨�Δ�(sh��)��(j��)�����d��CPLDоƬ�ϣ��ڲ���׃����(g��)ϵ�y(t��ng)Ӳ���B�ӵ���r�£�ݔ���Ñ�����IJ��Ρ���������CPLD���пɾ����������ԣ�������Է���ظ��Q���Δ�(sh��)��(j��)���Һ������У�����O�㡣

�D2.2-7 �����D

2.3 �{(di��o)ԇ����

2.3.1 CPLD��ʹ���������Ć��}

CPLDоƬ�ṩ�˺ܶ���(g��)�Դ���_�����˜p��оƬ��(n��i)���ĸɔ_���M����ÿ��(g��)�Դ���_̎��һ��(g��)��ź��ݣ�һ��һ��(g��)оƬ�܇�������6��(g��)��ݡ�

CPLD����������d�������ж�N���}���șz��оƬ�ĸ���(g��)�ӵ��_���Դ�_�Ƿ�ȫ���B�����_��Ȼ���Ă�(g��)JTAG���_�Ƿ��B�����_���������d�r(sh��)�^�y�Ă�(g��)���_�ϵ���̖��

���ڲ�ʹ�õ�ȫ��׃��������B�ӵ��ؾ����ھ��g�ĕr(sh��)����ܕ����F(xi��n)���õ��T��(sh��)���࣬���Ǿ��gͨ���^����r������߉�C�ϵ��x�(xi��ng)�����O(sh��)��һ�¡�

��߉�C�ϵĕr(sh��)������x���O(sh��)Ӌ(j��)�h(hu��n)���Ќ����ض���оƬ���ṩ�ľC�ϗl����������ɲ���Ҫ���韩��

2.3.2 �����·���{(di��o)ԇ

�������·�M(j��n)�Еr(sh��)����棬�ڷ���D�Ў��������F(xi��n)�҂�������Ҫ��ë�̣��@Щë���Еr(sh��)���oϵ�y(t��ng)����������Ӱ푣��҂���횲�ȡ��ʩ�����@�ӵ�ë�̡�����ë��һ����F(xi��n)����̖�l(f��)���ƽ�D(zhu��n)�Q�ĕr(sh��)�̣�Ҳ��ݔ����̖�Ľ����r(sh��)�g��(n��i)������ݔ����̖�ı��֕r(sh��)�g��(n��i)��������F(xi��n)����ˣ�����ë�̵���̖���m(x��)�r(sh��)�g�^�L���҂�����ݔ����̖�ij��m(x��)�r(sh��)�g��(n��i)��һ�����ȵĸ��ƽ�}�_�xͨһ��(g��)�c�T���@��ԓ��̖���˕r(sh��)ë����Ȼ�ѱ����������ƽ�}�_����ܛ�������i�������õ�������ë�̵���̖���֕r(sh��)�g�^�̣�������D�|�l(f��)����Dݔ��ˌ�ë�̲����е����c(di��n)����ݔ����̖�ı��֕r(sh��)�g��(n��i)���|�l(f��)���xȡݔ����̖���˕r(sh��)ë����ȻҲ�ѱ��������|�l(f��)���ĕr(sh��)��ؿ���ܛ�����Ƶ�ַ�g�a�����õ���

���� ����ijЩ��r�£���Ҫ����̖�M(j��n)��һ�����ӕr(sh��)��������ض��Ĺ��ܡ�����D�|�l(f��)�����ڕr(sh��)犵Ŀ�������̖�M(j��n)�б��^���_���ӕr(sh��)���@�N��������С�ӕr(sh��)�ǰ낀(g��)�r(sh��)����ڡ��ӕr(sh��)Ҳ������ë�̵��ֶ�֮һ��

2.3.3 DAC�·���{(di��o)ԇ

DAC�·��RAM���ұ�ݔ�����xɢ�Ĕ�(sh��)����̖׃�Q���B�m(x��)��ģ�M��̖�����x��оƬ��DAC0832�����ķֱ��ʞ�12bits�������r(sh��)�g��1us��������ݔ����ݔ�������2-20mA��(n��i)���{(di��o)����������o��ֱ�Ӝy����������DAC0832��ݔ���˺͵�֮�g����һ��(g��)20�W����裬�Ɍ�ݔ��������D(zhu��n)�Q��늉���y���^�����£�������DACݔ��ȫ1�Ĕ�(sh��)��(j��)���y��ݔ����11�_��늉���0.4V��12�_��0.04 V������DACݔ��ȫ0�Ĕ�(sh��)��(j��)���y��ݔ���˹�11�_��늉���0.04 V��12�_��0.4V���f��DAC�·����������

2.3.4 ������{(di��o)ԇ

�O(sh��)Ӌ(j��)��ʹ����ALTERA��˾�ṩ������ܛ��MAX+PLUSII�M(j��n)���ļ���ݔ�롢���g�����d��MAX+PLUSII��ܛ���O(sh��)Ӌ(j��)��Ҫ���O(sh��)Ӌ(j��)ݔ�롢�(xi��ng)Ŀ���g���(xi��ng)ĿУ�(y��n)���������̵��IJ��֘�(g��u)�ɡ�

2.3.5 Ӳ���·���{(di��o)ԇ

��Ӳ���·�{(di��o)ԇ�У�Ҫע�⺸�ӵ�ˇ�g(sh��)��Ԫ���IJ��֣����w�@�����^�����ܳ��F(xi��n)©�����e(cu��)���ȬF(xi��n)���ڟ�������֮���·�M(j��n)�Мyԇ�����·�Ƿ����_(d��)���A(y��)�ڵĹ��ܡ�������ܣ��tҪ�M(j��n)�г�����{(di��o)ԇ�����z�y�·�B�ӡ�Ԫ��ʹ�õȷ���Ć��}��Ŭ���ų����ϣ�ϵ�y(t��ng)���܌�(sh��)�F(xi��n)��

�Y(ji��) Փ

Փ���л���CPLD�IJ�����̖�l(f��)���������M(j��n)�����O(sh��)Ӌ(j��)�������˰������Dz������Ҳ��������������̖�IJ��Ύ죬�鲨�ε��x���ṩ���^�õIJ���ƽ�_����DDS���g(sh��)�cCPLD���g(sh��)��Y(ji��)�ρ��O(sh��)Ӌ(j��)���ನ�ΰl(f��)������ʹ���N��̖��ݔ����λ�����120o�����·��(sh��)�ֲ�������˷ֲ����ܷ���Ͳ��η��棬Ŭ�����Ɣ�(sh��)�ֲ��ΰl(f��)�����Ļ�����̖��������(sh��)�F(xi��n)�·�ļ��ɻ��������pRAM�pͨ��ʹ�O(sh��)Ӌ(j��)���Ĕ�(sh��)�ֲ��ΰl(f��)�����и�����m�÷��������O(sh��)Ӌ(j��)�ܑ�(y��ng)�õ��̌W(xu��)�Ϳ���ԇ�(y��n)�С�

�ڷ�����DDS��CPLD���g(sh��)�Ļ��A(ch��)�ϣ��O(sh��)Ӌ(j��)��һ�N����CPLD��������(sh��)�ֲ��ΰl(f��)����������CPLD�_�l(f��)���ߌ��·�M(j��n)�����O(sh��)Ӌ(j��)�ͷ��棬�ķ��x������ϵ�y(t��ng)�ֲ���ÿһ������(j��ng)�^�ˇ�(y��n)��IJ��η����(y��n)�C���Դ_������������

���ĽY(ji��)�����Ⲩ�ΰl(f��)�����İl(f��)չ?f��n)�r����ֱ�Ӕ�(sh��)�ֲ��κϳɼ��g(sh��)����Փ���O(sh��)Ӌ(j��)�������·��(sh��)�F(xi��n)�Լ���̖���{(di��o)���·�M(j��n)����������о����w�{������Ҫ����������Ĺ�����1������CPLD�����O(sh��)Ӌ(j��)��ֱ�Ӕ�(sh��)�ֺϳɼ��g(sh��)оƬ��ͨ�^�ˌ�(sh��)�(y��n)�(y��n)�C��2���O(sh��)Ӌ(j��)�˃�(n��i)�{(di��o)���·��3���O(sh��)Ӌ(j��)�{(di��o)ԇ��̖�{(di��o)���·��4�������ˌ�(sh��)�(y��n)�C(j��)�������Δ�(sh��)��(j��)ݔ������

�����w�Ͽ������x������(sh��)�F(xi��n)��ָ��(bi��o)�����ϝM���n�}Ҫ��ͬ�r(sh��)Ҳ�������������Ҫ�M(j��n)һ�����M(j��n)�Ĺ�������Ҫ�w�F(xi��n)�ڣ�1���{(di��o)�l�����Ⲩ�l���·��Ҫ�M(j��n)һ�����M(j��n)�����ø�λ���i��h(hu��n)������2��ܛ����Ӳ���·�O(sh��)Ӌ(j��)�����]��ȫ����ɣ�3�����ڼ��g(sh��)���ƣ�ϣ���Ժ���ʹ����ݔ���l����һ��(g��)�����_�A��

���ǣ�Ҳ������ijЩ���㡣���磺��(d��ng)�r(sh��)�����_�l(f��)���ںͼ��g(sh��)ˮƽ��ԭ��DDS���g(sh��)�������ˇ�����͵ļ���оƬ�����H���r(ji��)�ߣ������S�����ܛ]�г�����ã��{(di��o)��������Ҳ����ߡ�

ͨ�^���I(y��)�n�}�O(sh��)Ӌ(j��)��������ֱ�Ӳ��κϳɼ��g(sh��)��ԭ�����O(sh��)Ӌ(j��)Ҫ�I(l��ng)���W(xu��)��(x��)�˲����տɾ���߉�����·���O(sh��)Ӌ(j��)��������MAX+PLUSIIܛ����CPLDԪ���ȵđ�(y��ng)�ã�����˜\�����ҽ��Ĺ����͌W(xu��)��(x��)�춨�ˈ�(ji��n)��(sh��)�Ļ��A(ch��)��

�����īI(xi��n)

[1]����ɽ.EDA���g(sh��)���ɾ���������(y��ng)�Õr(sh��)Ӗ(x��n)[M].����:�ƌW(xu��)������.2003

[2]������.��(f��)�s�ɾ���߉�����c��(y��ng)���O(sh��)Ӌ(j��)[M].����:�Ї��V�I(y��)��W(xu��)������.2003

[3]����飬����ɽ��.�ɾ�������EDA���g(sh��)�c��(sh��)�`[M].����:�C(j��)е���I(y��)������.2004

[4]�ّ.CPLD/FPGA�cASIC�O(sh��)Ӌ(j��)��(sh��)�`�̳�[M].����:�ƌW(xu��)������.2004

[5]������.����O(sh��)Ӌ(j��)[M].����:�ߵȽ���������.2003

[6]��|��.����O(sh��)Ӌ(j��)�Ԅӻ��cIC�O(sh��)Ӌ(j��)[M].����:�ߵȽ���������.2004

[7]����.EDA���g(sh��)��(sh��)�ý̳�[M].����:�C(j��)е���I(y��)������.2005

[8]����꣬����A��.EDA�O(sh��)Ӌ(j��)�c���挍(sh��)�`[M].����:�C(j��)е���I(y��)������.2004

[9]������.EDA���g(sh��)�c��(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)[M].���:������ӿƼ���W(xu��)������.2003

[10]̶��������������.EDA���g(sh��)�c��(y��ng)�ã��ڶ��棩[M].���:������ӿƼ���W(xu��)������.2004

[11]���揊(qi��ng).��ӌ�(sh��)�H�Ԅӻ���EDA�����g(sh��)��(sh��)�(y��n)�̳�[M].ɽ�|:ɽ�|��W(xu��)������.2003

[12]������.EDA���g(sh��)����(y��ng)��[M].����:���A��W(xu��)������.2004

[13]���GƼ��������.EDA��(sh��)�ü��g(sh��)����(y��ng)��[M].����:�������I(y��)������.2005

[14]������.EDA��(y��ng)�ü��g(sh��)[M].����:���A��W(xu��)������.2004

[15]���ɣ��S�^�I(y��)��.EDA���g(sh��)�cVHDL[M].����:���A��W(xu��)������.2003

[16]��ɏ.����CPLD�ĺ���(sh��)��̖�l(f��)����[J].��������.ɳ��ߵȎ������ƌW(xu��)Ժ�W(xu��)��(b��o). 2006,(5).15-18

[17]������.����CPLD�Ķನ�κ���(sh��)��̖�l(f��)�����O(sh��)Ӌ(j��)[J].�F(xi��n)����Ӽ��g(sh��).2006����17��.70-72

[18] Wu Tao��Wang Jian Hua et al. Application study of DSP and CPLD technology on the star sensor[J].Journal of Harbin Institute of Technology(New Series)��Vo1.13��No.3��2006.289-293

[19]�ξw��,�w��μ��. ����CPLD�͆�Ƭ�C(j��)�����Ⲩ�ΰl(f��)�����O(sh��)Ӌ(j��)[J].��Ӯa(ch��n)Ʒ����.2005,(1).118-119

[20] ����ϲ������.CPLD������ನ�κ���(sh��)�l(f��)�����O(sh��)Ӌ(j��)[J].�������Ԫ����.2006��

��4��.23-25

���1 ����ನ�κ���(sh��)�l(f��)������ģ�K�ij���

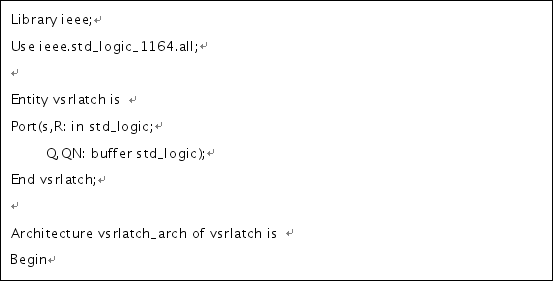

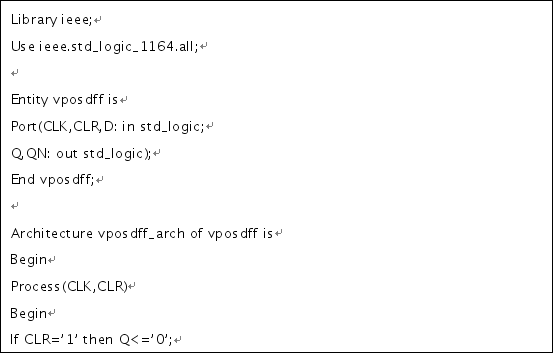

LIBRARY ieee ; -----��ֵģ�K

use ieee.std_logic_1164.all;

entity chuzhi is

port(a:in std_logic_vector(3 downto 0);

q:out integer range 0 to 312);

end chuzhi;

architecture chu_arc of chuzhi is

begin

process(a)

begin

case a is

when"0001"=>q<=313;

when"0010"=>q<=156;

when"0011"=>q<=104;

when"0100"=>q<=78;

when"0101"=>q<=63;

when"0110"=>q<=52;

when"0111"=>q<=45;

when"1000"=>q<=39;

when"1001"=>q<=35;

when"1010"=>q<=31;

when others=>null;

end case;

end process;

end chu_arc;

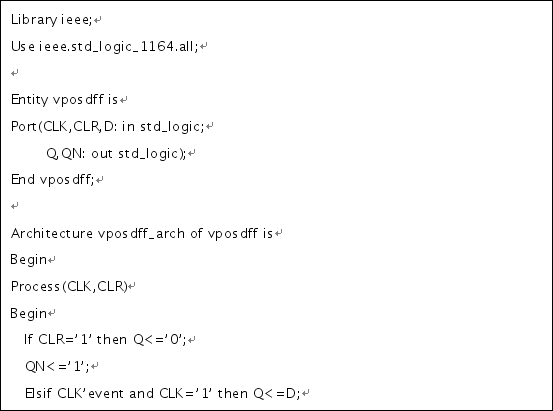

LIBRARY ieee ; ----���lģ�K

use ieee.std_logic_1164.all;

entity fana is

port(a:in integer range 0 to 312;

clk:in std_logic;

q:out std_logic);

end fana;

architecture fan_arc of fana is

begin

process(clk)

variable b,d:std_logic;

variable c:integer range 0 to 312;

begin

if clk'event and clk='1'then

if b='0'then

c:=a-1;

b:='1';

else

if c=1 then

b:='0';

d:=not d;

else

c:=c-1;

end if;

end if;

end if;

q<=d;

end process;

end fan_arc;

LIBRARY ieee; -----����ģ�K

use ieee.std_logic_1164.all;

entity square is

port(clk,clr:in std_logic;

q:out integer range 0 to 255);

end square;

architecture sq_arc of square is

signal a:bit;

begin

process(clk,clr)

variable cnt:integer;

begin

if clr='0'then

a<='0';

elsif clk'event and clk='1'then

if cnt<7 then

cnt:=cnt+1;

else

cnt:=0;

a<=not a;

end if;

end if;

end process;

process(clk,a)

begin

if clk'event and clk='1'then

if a='1'then

q<=255;

else

q<=0;

end if;

end if;

end process;

end sq_arc;

LIBRARY ieee;------���Dz�ģ�K

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity delta is

port(clk,reset:in std_logic;

q:out std_logic_vector(7 downto 0));

end delta;

architecture delta_arc of delta is

begin

process(clk,reset)

variable tmp:std_logic_vector(7 downto 0);

variable a:std_logic;

begin

if reset='0' then

tmp:="00000000";

elsif clk'event and clk='1' then

if a='0'then

if tmp="11111000"then

tmp:="11111111";

a:='1';

else

tmp:=tmp+8;

end if;

else

if tmp="00000111"then

tmp:="00000000";

a:='0';

else

tmp:=tmp-8;

end if;

end if;

end if;

q<=tmp;

end process;

end delta_arc;

LIBRARY ieee; ------���Ҳ�ģ�K

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity delta is

port(clk,reset:in std_logic;

q:out std_logic_vector(7 downto 0));

end delta;

architecture delta_arc of delta is

begin

process(clk,reset)

variable tmp:std_logic_vector(7 downto 0);

variable a:std_logic;

begin

if reset='0' then

tmp:="00000000";

elsif clk'event and clk='1' then

if a='0'then

if tmp="11111000"then

tmp:="11111111";

a:='1';

else

tmp:=tmp+8;

end if;

else

if tmp="00000111"then

tmp:="00000000";

a:='0';

else

tmp:=tmp-8;

end if;

end if;

end if;

q<=tmp;

end process;

end delta_arc;

LIBRARY ieee;------����ģ�K

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity chpro31 is

port(dlt,sqr,sin:in std_logic;

dlta,sqra,sina:in std_logic_vector(7 downto 0);

q:out std_logic_vector(7 downto 0));

end chpro31;

architecture ch_arc of chpro31 is

begin

process(dlt,dlta,sqr,sqra,sin,sina)

variable tmp:std_logic_vector(2 downto 0);

variable a,b:std_logic_vector(9 downto 0);

variable c,d,e:std_logic_vector(9 downto 0);

begin

tmp:=dlt&sqr&sin;

case tmp is

when "100"=>q<=dlta;

when "010"=>q<=sqra;

when "001"=>q<=sina;

when "110"=>a:="00"&dlta+sqra;

q<=a(8 downto 1);

when "101"=>a:="00"&dlta+sina;

q<=a(8 downto 1);

when "011"=>a:="00"&sqra+sina;

q<=a(8 downto 1);

when "111"=>a:="00"&dlta+sqra;

b:=a+sina;

c:="00"&b(9 downto 2);

d:="0000"&a(9 downto 4);

e:="000000"&a(9 downto 6);

a:=c+d;

b:=a+e;

q<=b(7 downto 0);

when others=>null;

end case;

end process;

end ch_arc;

���2 Ԫ����B

1 DAC0832

DAC0832 ��һ�N�ஔ(d��ng)�ձ��ҳɱ��^�͵Ĕ�(sh��)/ģ�D(zhu��n)�Q����ԓ������һ��(g��)8λD/A�D(zhu��n)�Q�������D(zhu��n)�Q�r(sh��)�g��1s������늉���+5V��+15V������(zh��n)늉����10V������һ��(g��)8λ�Ķ��M(j��n)�Ɣ�(sh��)�D(zhu��n)�Q��ģ�M늉����ɮa(ch��n)��256�N��ͬ��늉�ֵ���������(n��i)���Ѓɂ�(g��)8λ�Ĵ�����һ��(g��)8λD/A�D(zhu��n)�Q�����ʿ��M(j��n)�Ѓɼ����_������ʹ�����кܴ���`����(���O(sh��)Ӌ(j��)�в��õ��džξ��_��ʽ)��

DAC0832����������Ҫ���ԣ��ٝM��TTL�ƽҎ(gu��)����߉ݔ�룻�ڷֱ��ʞ�8λ�� �۽����r(sh��)�g��1us���ܹ���20mw�����������ݔ����D/A�D(zhu��n)�Q�����ڑ�(y��ng)�Õr(sh��)����\(y��n)��ʹ֮�ɞ�늉���ݔ����DAC0832��Ƭ�x��ַ��7FFFH����(d��ng)P27��Ч�r(sh��)����P0�������͵Ĕ�(sh��)��(j��)��00H���tU ��ݔ��늉���0V����P0�������͵Ĕ�(sh��)��(j��)��0FFH�r(sh��)���t��ݔ��늉���-5V���ʮ�(d��ng)ݔ��늉���0V�r(sh��)��Vo��-5V����(d��ng)ݔ��늉���-5V�r(sh��)���ɵã�Vo =+5V������ݔ�����ε�늉�׃��������-5V ��+5V���B��Ӳ���·�r(sh��)���ɼ��Ĵ����Ŀ�����̖����ݔ�딵(sh��)��(j��)���ڿ�����̖������ֱ������DAC�Ĵ����С���(j��ng)D/A�D(zhu��n)�Q�ͷ��ȿ��ƣ��ٞV�����ɵõ����Ρ�

�D1 DAC0832��(n��i)���Y(ji��)��(g��u)��D��ʾ

�D2 DAC0832

2 LM324

LM324���\(y��n)��������national��˾�Įa(ch��n)Ʒ��LM324�����\(y��n)�ż����·,������14�_�p��ֱ�����Ϸ��b�����ă�(n��i)�������ĽM��ʽ��ȫ��ͬ���\(y��n)��Ŵ���, ���Դ������,�ĽM�\(y��n)�����(d��)����ÿһ�M�\(y��n)��Ŵ������ÈD1��ʾ�ķ�̖����ʾ,����5��(g��)�����_,���С�+������-����ɂ�(g��)��̖ݔ���,��V+������V-��������ؓ(f��)�Դ��,��Vo����ݔ���ˡ��ɂ�(g��)��̖ݔ�����,Vi-��-���鷴��ݔ���,��ʾ�\(y��n)��ݔ����Vo����̖�cԓݔ��˵�λ�෴;Vi+��+����ͬ��ݔ���,��ʾ�\(y��n)��ݔ����Vo����̖�cԓݔ��˵���λ��ͬ��

����LM324���\(y��n)���·�����Դ늉�������,�o�B(t��i)����С,�Ɇ��Դʹ��,�r(ji��)������ȃ�(y��u)�c(di��n),��˱��V����(y��ng)���ڸ��N�·�С�

�ڱ�ϵ�y(t��ng)�У�LM324������Ŵ����͞V������ʹ�á��������x������(g��)��ͬ�l�ε���̖,ָʾ����̖���ȵĴ�С������̖�M(j��n)�зŴ����ݔ�����ṩ�oʹ������Ҫ�IJ�����̖��

�D3 LM324���_�D

3 PM7128SLC84-15оƬ

EPM7128S84-15��CPLDоƬ����128��(g��)���Ԫ��2500��(g��)��Ч߉�T��15ns���ٶȡ�PLCC84���b��ʽ�����Դ���_���ؾ����_��ȫ�ֿ������_��JTAG���_�⣬���ṩ��64��(g��)����I/O�_���@Щ���_�����������Þ�ݔ�롢ݔ�����p��ʽ��ԓ���������c(di��n)����:

l�� һ �N�����ܵ�CM0SE EPROM������

l�� �� ��ͨ�^JTAG�ӿڌ�(sh��)�F(xi��n)�ھ����̡�

l��(n��i) ��JTAG BST�·��

l�� �� �̺��Ԫ�|�l(f��)�����Ќ����������λ���r(sh��)犺͕r(sh��)�ʹ�ܿ��ơ�

l �� �� �õĔU(ku��)չ�˷e�(xi��ng)���䣬���S��ÿ��(g��)���Ԫ�ṩ���_(d��)32��(g��)�˷e�(xi��ng)��

�D4EPM7128SLC84-15

���3�·ԭ��D

���4 Ӣ���Y�ϼ��g��

1Ӣ���Y��

(From DIGITAL DESIGN principles & practices ,John F. Wakerly)

Language Overview

What is VHDL?

VHDL is a programming language that has been designed and optimized for describing the behavior of digital systems.

VHDL has many features appropriate for describing the behavior of electronic components ranging from simple logic gates to complete microprocessors and custom chips. Features of VHDL allow electrical aspects of circuit behavior (such as rise and fall times of signals, delays through gates, and functional operation) to be precisely described. The resulting VHDL simulation models can then be used as building blocks in larger circuits (using schematics, block diagrams or system-level VHDL descriptions) for the purpose of simulation.

VHDL is also a general-purpose programming language: just as high-level programming languages allow complex design concepts to be expressed as computer programs, VHDL allows the behavior of complex electronic circuits to be captured into a design system for automatic circuit synthesis or for system simulation. Like Pascal, C and C++, VHDL includes features useful for structured design techniques, and offers a rich set of control and data representation features. Unlike these other programming languages, VHDL provides features allowing concurrent events to be described. This is important because the hardware described using VHDL is inherently concurrent in its operation.

One of the most important applications of VHDL is to capture the performance specification for a circuit, in the form of what is commonly referred to as a test bench. Test benches are VHDL descriptions of circuit stimuli and corresponding expected outputs that verify the behavior of a circuit over time. Test benches should be an integral part of any VHDL project and should be created in tandem with other descriptions of the circuit.

A standard language

One of the most compelling reasons for you to become experienced with and knowledgeable in VHDL is its adoption as a standard in the electronic design community. Using a standard language such as VHDL virtually guarantees that you will not have to throw away and recapture design concepts simply because the design entry method you have chosen is not supported in a newer generation of design tools. Using a standard language also means that you are more likely to be able to take advantage of the most up-to-date design tools and that you will have access to a knowledge base of thousands of other engineers, many of whom are solving problems similar to your own.

A brief history of VHDL

VHDL, which stands for VHSIC (Very High Speed Integrated Circuit) Hardware Description Language, was developed in the early 1980s as a spin-off of a high-speed integrated circuit research project funded by the U.S. Department of Defense. During the VHSIC program, researchers were confronted with the daunting task of describing circuits of enormous scale (for their time) and of managing very large circuit design problems that involved multiple teams of engineers. With only gate-level design tools available, it soon became clear that better, more structured design methods and tools would be needed.

To meet this challenge, a team of engineers from three companies ?IBM, Texas Instruments and Intermetrics ?were contracted by the Department of Defense to complete the specification and implementation of a new, language-based design description method. The first publicly available version of VHDL, version 7.2, was released in 1985. In 1986, the Institute of Electrical and Electronics Engineers, Inc. (IEEE) was presented with a proposal to standardize the language, which it did in 1987 after substantial enhancements and modifications were made by a team of commercial, government and academic representatives. The resulting standard, IEEE 1076-1987, is the basis for virtually every simulation and synthesi product sold today. An enhanced and updated version of the language, IEEE 1076-1993, was released in 1994, and VHDL tool vendors have been responding by adding these new language features to their products.

Although IEEE Standard 1076 defines the complete VHDL language, there are aspects of the language that make it difficult to write completely portable design descriptions (descriptions that can be simulated identically using different vendors?tools). The problem stems from the fact that VHDL supports many abstract data types, but it does not address the simple problem of characterizing different signal strengths or commonly used simulation conditions such as unknowns and high-impedance.

Soon after IEEE 1076-1987 was adopted, simulator companies began enhancing VHDL with new, non-standard types to allow their customers to accurately simulate complex electronic circuits. This caused problems because design descriptions entered into one simulator were often incompatible with other simulation environments. VHDL was quickly becoming a nonstandard.

To get around the problem of nonstandard data types, another standard was developed by an IEEE committee. This standard, numbered 1164, defines a standard package (a VHDL feature that allows commonly used declarations to be collected into an external library) containing definitions for a standard nine-valued data type. This standard data type is called std_logic, and the IEEE 1164 package is often referred to as the Standard Logic package.

The IEEE 1076-1987 and IEEE 1164 standards together form the complete VHDL standard in widest use today. (IEEE 1076-1993 is slowly working its way into the VHDL mainstream, but it does not add significant new features for synthesis users.)

Standard 1076.3(often called the Numeric Standard or Synthesis Standard) defines standard packages and interpretations for VHDL data types as they relate to actual hardware. This standard, which was released at the end of 1995, is intended to replace the many custom (nonstandard) packages that vendors of synthesis tools have created and distributed with their products.

IEEE Standard 1076.3 does for synthesis users what IEEE 1164 did for simulation users: increase the power of Standard 1076, while at the same time ensuring compatibility between different vendors?tools. The 1076.3 standard includes, among other things:

1) A documented hardware interpretation of values belonging to the bit and boolean types defined by IEEE Standard 1076, as well as interpretations of the std_ulogic type defined by IEEE Standard 1164.

2) A function that provides "don&care" or "wild card" testing of values based on the std_ulogic type. This is of particular use for synthesis, since it is often helpful to express logic in terms of "don�t care" values.

3) Definitions for standard signed and unsigned arithmetic data types, along with arithmetic, shift, and type conversion operations for those types.

The annotation of timing information to a simulation model is an important aspect of accurate digital simulation. The VHDL 1076 standard describes a variety of language features that can be used for timing annotation. However, it does not describe a standard method for expressing timing data outside of the timing model itself.

The ability to separate the behavioral description of a simulation model from the timing specifications is important for many reasons. One of the major strengths of Verilog HDL (VHDL�s closest rival) is the fact that Verilog HDL includes a feature specifically intended for timing annotation. This feature, the Standard Delay Format, or SDF, allows timing data to be expressed in a tabular form and included into the Verilog timing model at the time of simulation.

The IEEE 1076.4 standard, published by the IEEE in late 1995, adds this capability to VHDL as a standard package. A primary impetus behind this standard effort (which was dubbed VITAL, for VHDL Initiative Toward ASIC Libraries) was to make it easier for ASIC vendors and others to generate timing models applicable to both VHDL and Verilog HDL. For this reason, the underlying data formats of IEEE 1076.4 and Verilog SDF are quite similar.

When should you use VHDL?

Why choose to use VHDL for your design efforts? There are many likely reasons. If you ask most VHDL tool vendors this question, the first answer you will get is, "It will improve your productivity." But just what does this mean? Can you really expect to get your projects done faster using VHDL than by using your existing design methods?

The answer is yes, but probably not the first time you use it, and only if you apply VHDL in a structured manner. VHDL (like a structured software design language) is most beneficial when you use a structured, top-down approach to design. Real increases in productivity will come later, when you have climbed higher on the VHDL learning curve and have accumulated a library of reusable VHDL components.

Productivity increases will also occur when you begin to use VHDL to enhance communication between team members and when you take advantage of the more powerful tools for simulation and design verification that are available. In addition, VHDL allows you to design at a more abstract level. Instead of focusing on a gate-level implementation, you can address the behavioral function of the design.

How will VHDL increase your productivity? By making it easy to build and use libraries of commonly-used VHDL modules. VHDL makes design reuse feel natural. As you discover the benefits of reusable code, you will soon find yourself thinking of ways to write your VHDL statements in ways that make them general purpose. Writing portable code will become an automatic reflex.

Another important reason to use VHDL is the rapid pace of development in electronic design automation (EDA) tools and in target technologies. Using a standard language such as VHDL can greatly improve your chances of moving into more advanced tools (for example, from a basic low-cost simulator to a more advanced one) without having to re-enter your circuit descriptions. Your ability to retarget circuits to new types of device targets (for example, ASICs, FPGAs, and complex PLDs) will also be improved by using a standard design entry method.

Most of the VHDL features that are needed to support sequential-circuit design, in particular, processes, were already introduced in section 4.7 and were used in the VHDL sections in chapter 5. This section introduces just a couple more features and gives simple examples of how they are used .Larger examples appear in the VHDL sections of chapter

8. feedback sequential circuits

A VHDL process and the simulator��s event-list mechanism for tracking signal changes form the sequential circuits may change state in response to input changes , and these state changes are manifested by changes propagating in a feedback loop until the feedback loop stabilizes. In simulation, this is manifested by the simulator putting signal changes on the event list and scheduling processes to return in ��delta time�� and propagating these signal changes until to no more signal changes are scheduled.

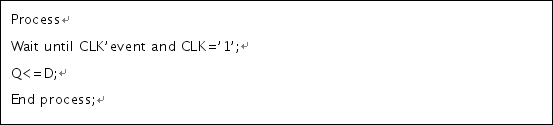

Table 7-36 dataflow VHDL for an S-R latch.

Table 7-36 is a VHDL program for an S-R latch, the architecture contains two concurrent assignment statements. Each of which gives rise to a process, as discussed in section 4.7.9, these processes interact to create the simple latching behavior of a S-R latch.

The VHDL simulation is faithful enough to handle the case where both S and R are asserted simultaneously. The most interesting result in simulation occurs if you negate S and R simultaneously. Recall from the box from the page 536 that a real S-R latch may oscillate or go into a metastable state in this simulation. The simulation will potentially loop forever as each execution of one assignment statement triggers another execution of the other. After some number of repetitions, a well-designed simulator will discover the problem----delta time keeps advancing while simulated time does not----and halt the simulation.

WHAT DO ��U�� WANT

It would be nice if the S-R latch model in table 7-36 produced a ��u�� output whenever S and R were negated simultaneously, but it��s not that good. However, the languages is powerful enough that experienced VHDL designers can easily write a model with that behavior. Such a model would make use of VHDL��s time-modeling facilities, which we haven��t discussed, to model the latch��s ��recovery time�� (see box in page 537) and force a ��u�� output if a second input change occurred too soon. It��s even possible to model a maximum assumed metastability resolution time in this way.

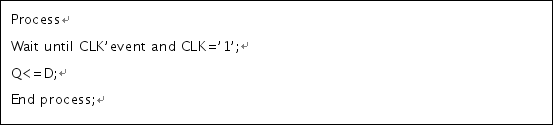

Table 7-37 behavioral VHDL for a positive-edge-triggered D flip-flop

Mote that if a circuit has the possibility of entering a metatable state, there��s no

guarantee that the simulation will detect it, especially in larger designs. The best way to avoid metasbgability problems in a system design is to clearly identify and protect its asynchronous boundaries, as discussed in section clocked circuits

In practice, the majority of digital designs that are modeled using VHDL are clocked, synchronous systems using edge-triggered flip-flops. In addition to what we��ve already learned about VHDL, there��s just one more feature needed to describe edge-triggered behavior. The event attribute attached to a signal name to yield a value of type Boolean that is true if an event on the signal caused the encompassing process to run in the current simulation cycle, and false otherwise.

Using the event attribute, we can model the behavior of a positive-edge-triggered D flip-flop with asynchronous clear as shown in table 7-37. here, the asynchronous clear input CLR overrides any behavior on the clock input CLK and is therefore checked first, in the ��if�� clause. If CLR is negated, then the ��elsif�� clause is checked, and its statements are executed on the rising edge of CLK. Note that ��CL��event�� is true for any change on CLK, and ��CLK=��1���� is checked to limit triggering to just the rising edge of CLK. There are many other ways to construct processes or statements with edge-triggered behavior; table 7-38 shows two more ways to describe a D flip-flop ( without a CLR input ).

Table 7-38 two more ways to describe a positive-edge-triggered D flip-flop.

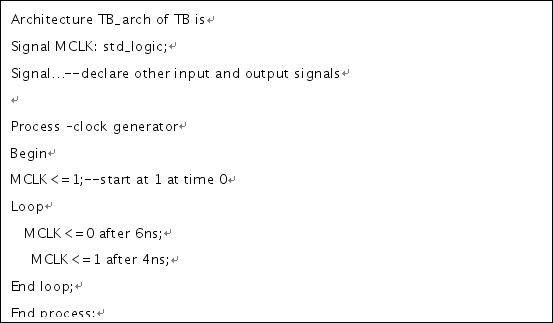

In the test bench for a clocked circuit, one of things you need to do is generate a system clock signal. This can be done quite easily with a loop inside a process, as shown in table 7-39 for a 100MHz clock with a 60% duty cycle.

*****SYNTHESIS STUFF*****

You may be wondering, how does a synthesis tool convert the edge-triggered behavior described in table 7-37 or 7-38 into an efficient flip-flop realization? Most tools recognize only a few predetermined ways of expressing edge-triggered behavior and map those into predetermined flip-flop components in the target technology.

The synopsis synthesis engine used in the xinlinx foundation series 1.5 software recognize the��clk��event and clk=��1���� expression that we use in this book. Even with that as a given, VHDL has many different ways ashenden, author of the designer��s guide to

VHDL (morgan Kaufmann, 1996) ran these statements and one other, with some modification, through several different synthesis tools. Only one of them was able to synthesize three out of the four forms, most could handle only two. So, you need to follow the method that is prescribed by the tool you use.

Table 7-39 clock process within a test bench.

reference

The problem of metastability has been around for a long time. Greek philosophers wrote about the problem of indecision thousands of years ago. A group of modem philosophers named Devon sang about metastability in the title song of their Freedom of choice album. And the u.s. congress still can��t decide how to ��save�� social security.

Scan capability was first deployed in latches. Not flip-flop, in IBM IC designs decades ago. Edward J.McCluskey has a very good discussion of this and other scan methods in logic design principles (prentice hall, 1986).

Most ASICs and MSI-,PLD- and FPGA-based designs use the sequential circuit types described in this chapter. However , there are other types that are use in both older discrete designs (going all the way back to vacuum-tube logic ) and as well as in modem, custom VLSI designs.

For example, clocked synchronous state machines are a special case of a more general class of pulse-mode circuits, Such circuits have one or more pulse inputs such that (a) only one pulse occurs at a time; (b) non-pulse inputs are stable when a pulse occurs; (c) only pulses can cause state changes; and (d) a pulse clock is the single pulse input, and a ��pulse�� is the triggering edge of the clock. However, it is also possible to build circuits with multiple pulse inputs. These possibilities are discussed very thoroughly in McCluskey��s logic Design Principle (prentice hall, 1986).

A particularly important type of pulse-mode circuit that is discussed by McCluskey and others is the two-phase latch machine. The rationale for a two phase clocking approach in VLSI circuits is discussed by Carver Mead and Lynn Conway in introduction to VLSI systems (Addison-Wesley, 1980). There machines essentially eliminate the essential hazards present in edge-triggered flip-flops by using pairs of latches that are enabled by no overlapping clocks.

Methods for reducing both completely and incompletely specified state tables are described in advanced logic design texts, including McCluskey��s 1986 book. A more mathematical discussion of these methods and other ��theoretical�� topics in sequential machine design appears in switching and finite automata theory, second edition, by Zvi Kohavi (McFGraw-hall, 1978).

As we showed in this chapter, improperly constructed state diagrams may idle an ambiguous description of next-state behavior. The ��if-then-else�� structures in HDLs like ABEL and VHDL can eliminate these ambiguities, but they were not first to do so. Algorithmic-state-machine (ASM) notation. A flowchart-like equivalent of nested if-then-else statement, has been around for over 25 years. So-called ASM charts were pioneered at Hewlett-Packard Laboratories by Thomas E. Osborne and were pioneered by Osborne��s colleague Christopher R. Clare in a book, designing logic systems using ASM charts (McGraw-hill ,1973).Design and synthesis methods using ASM charts subsequently found a home in many digital design texts. Including the art of digital design by F.P.Prosser and D.E.Winkel (prentice hall, 1987, second edition ), and digital design by M.Morris Mano (prentice hall, 1984), as well as in the fist two editions of the book you��re just reading.

Another notation for describing state machines is an extension of ��traditional�� state-diagram notation called the mnemonic documented state (MDS) diagram. It was developed by William I.Fletcher in an engineering approach to digital design (prentice-hall. 1980). ASM charts and MDS diagrams have now been largely replaced by HDLs and their compilers.

Many CAD environments for digital design include a graphical state diagram entry tool. Unfortunately, these typically support only traditional state diagrams, making it very easy for a designer to create an ambiguous descriptions of next-state behavior. As a result, my personal recommendation is that you stay away from state-diagram editors and instead use an HDL to describe your state machines.

We mentioned the importance of synchronizing sequences in connections with state-machine test vectors. There��s actually a very well developed but almost forgotten theory and practice of synchronizing sequences and somewhat less powerful ��homing experiment�� described by Frederick C.Hennie in Finite-state Models for logical machines (Wiley, 1968) Unless you��ve got this old classic on your bookshelf and know how to apply its teachings, please just remember to provide a reset input in every state machine that you design!

2Ӣ���g��

�Z�Ը��^

VHDL��ʲô?

VHDL��һ�N�ѽ�(j��ng)���������ɞ���y(t��ng)���О��O(sh��)Ӌ(j��)��ѻ���Ҏ(gu��)���Z�ԡ�

��?y��n)����������ĺ��ε�߉�T������ӳɷݵ��О����̎��������(x��)�TҎ(gu��)���� VHDL �S�������m��(d��ng)��VHDL���������S��·�О� ( ���������������r(sh��)������̖�����t�^�T, ���ܵIJ���) ��늚����Ծ��_�ر�������Ȼ�����Ǯa(ch��n)����VHDL ģ�Mģ�͞���ģ�M�����^��ľ�· ( ʹ�ÈD��, �^(q��)�ΈD����ϵ�y(t��ng)���� VHDL ����) �б���(d��ng)����늚�^(q��)��ʹ�á�

VHDL Ҳ��һ�N�����͵�Ҏ(gu��)���Z�ԣ�������A�ӵ�Ҏ(gu��)���Z�����S��(f��)�s��Ҫ��ʾ����X��ʽ���O(sh��)Ӌ(j��)�^��, VHDL ���S��(f��)�s��ӵľ�·�О錦���Ԅӵľ�·�C�ϻ�ϵ�y(t��ng)ģ�M�M(j��n)��һ��(g��)�O(sh��)Ӌ(j��)ϵ�y(t��ng)֮��(n��i)�����@. ���˹���� C �� C++, VHDL �������Y(ji��)��(g��u)���O(sh��)Ӌ(j��)���g(sh��)�����õ�, �����ṩһ���нM�Ŀ��ƺ͔�(sh��)��(j��)���F(xi��n)�������������@Щ����������Ҏ(gu��)���Z�ԣ� VHDL �ṩ�������S�f(xi��)ͬ��Ҫ�������¼�����?y��n)鱻�������е�ʹ�?VHDL ��Ӳ�������IJ��������Džf(xi��)ͬ�ģ������@����Ҫ��

VHDL ������Ҫ��Ո֮һ�Ǟ�һ��(g��)��·���Ա��ձ�Q��һ���yԇ�L���ӵĖ|����ʽ���yԇ�L�����Ǿ�· stimuli ���S���r(sh��)�g���^ȥ���C��·���О錦��(y��ng)���A(y��)��ݔ���� VHDL �������yԇ�L���ӑ�(y��ng)ԓ��һ��(g��)�κ� VHDL Ӌ(j��)�������w���ݲ��ґ�(y��ng)ԓ�ں�������·������ǰ��v�ŵ��R܇�б��a(ch��n)����

һ�N��(bi��o)��(zh��n)���Z��

�����o�����ܵ�����֮һ��׃�ɵĽ�(j��ng)�(y��n)�������� VHDL ��������ӵ��O(sh��)Ӌ(j��)һ��(g��)��(bi��o)��(zh��n)��^(q��)�������á�ʹ��һ�N��(bi��o)��(zh��n)���Z�ԣ�����VHDL��(sh��)�ϱ��C��ֻ����?y��n)����ѽ?j��ng)�x����O(sh��)Ӌ(j��)�M(j��n)�뷽�������ڱ��^�µ������O(sh��)Ӌ(j��)������֧Ԯ���㌢���G��������ȡ���O(sh��)Ӌ(j��)�^�ʹ��һ�N��(bi��o)��(zh��n)���Z��Ҳ��ζ��������܉����������O(sh��)Ӌ(j��)���߶����㌢���ЙC(j��)���ӽ�һ��(g��)��(sh��)��ǧӋ(j��)�����Ĺ��̎���֪�R��, ������(d��ng)�е�һЩ�����ڽ�Q���}�Ķ���(sh��)������Լ��ġ�

VHDL �ĺ��̚vʷ

��1980������ڃ�(n��i)���� VHSIC( ����ټ����·) Ӳ�������Z�Ե� VHDL ���l(f��)չ�类�������������Tٝ���ĸ��ټ����·�о�Ӌ(j��)����һ��(g��)�������档�� VHSIC Ӌ(j��)���ĕr(sh��)���о��T�挦������ߴ� ( ���������ĕr(sh��)�g) �ľ�·ʹ��η�s�������ҹ����dz���ľ�·�O(sh��)Ӌ(j��)�������S��̎��F(tu��n)�(du��)�Ć��}������Ψһ���T���O(sh��)Ӌ(j��)�ɵõĹ���, ���ܿ�׃������������^�Y(ji��)��(g��u)���O(sh��)Ӌ(j��)�������ߕ�����Ҫ�ġ�

����Ҫӭ���@һ����(zh��n), һЩ����IBM ���¿��_˹���ߺ� Intermetrics���ҹ�˾�Ĺ��̎����������͂����һ��(g��)�µ�Ҏ(gu��)������Z�Ԟ���A(ch��)���O(sh��)Ӌ(j��)������������һ VHDL��7.2 ��Ĺ����ɵð汾���� 1985��1986�걻���棬����늚���ӹ��̎��f(xi��)��(IEEE) �cһ�����hһ��ʬF(xi��n)��(bi��o)��(zh��n)���Z�ԣ�������ߺ�������������Ҫ����֮���� 1987 ������һ�M���̘I(y��)�ģ������͌W(xu��)Ժ�Ĵ����M�ɵijɆT���x�a(ch��n)����IEEE 1076-1987��(bi��o)��(zh��n), ��(sh��)���@�ǽ�����۵�ÿ��(g��)ģ�M�C�Ϯa(ch��n)Ʒ�Ļ��A(ch��)���Z�ԣ� IEEE 1076-1993 ��һ��(g��)����(qi��ng)�Ͱ汾����1994����棬����VHDL���ߏS�̰��@Щ�µ��Z���������������Įa(ch��n)Ʒ�����ؑ�(y��ng)��

�mȻ IEEE��1076��(bi��o)��(zh��n)���x��������VHDL�Z��, ����ʹ����ȫ����ʽ���O(sh��)Ӌ(j��)�������Z�Է��������y��( ��ͬһ�ر�ģ�Mʹ�ò�ͬ�ďS������Ӳ������)�����}��Դ�� VHDL ֧���S��ժҪ��(sh��)��(j��)��ͣ�����������δ֪��(sh��)���迹����˵IJ�ͬ��̖�������ձ�ʹ���^��ģ�M����ʾ���Ά��}����ɫ��l�����\(y��n)�С�

�� IEEE 1076-1987 �Dz��ò��ú�ģ�M����˾�_ʼ�����ַǘ�(bi��o)��(zh��n)��� VHDL ������S�����Ŀ͑����_��ģ�M�ϳ�����Ӿ�·����?y��n)��O(sh��)Ӌ(j��)���cһ��(g��)ģ�M���r(sh��)����������������ģ�M�h(hu��n)����ƥ�䣬�����@�����ˆ��}. VHDL ���ںܿ��׃��һ�N�ǘ�(bi��o)��(zh��n)�Ę�(bi��o)��(zh��n)��

����Ҫ��Q�ǘ�(bi��o)��(zh��n)��(sh��)��(j��)��͵Ć��}, ����Ę�(bi��o)��(zh��n)��һ��(g��) IEEE ί�T���l(f��)չ�ˡ��@һ��(g��)��(bi��o)��(zh��n)��1164 ̖, ���xһ��(g��)��(bi��o)��(zh��n)�ij����(���SҪ�ռ����ձ�ʹ���^�Ĺ����M(j��n)�����һ�g�ⲿ�ĈD���^֮��(n��i)��һ��(g��)VHDL����) �������x��һ��(g��)��(bi��o)��(zh��n)�ĵĔ�(sh��)��(j��)��͡��@�N��(bi��o)��(zh��n)�Ĕ�(sh��)��(j��)��ͽ���std_logic������IEEE 1164 ��(sh��)��(j��)���r(sh��)�����Q���(bi��o)��(zh��n)��߉����

IEEE 1076-1987��IEEE.1164��(bi��o)��(zh��n)һ���ڽ���V����ʹ�����γ��������� VHDL ��(bi��o)��(zh��n)�� (IEEE 1076-1993 ������ʹ�����O(sh��)Ӌ(j��)�����M(j��n) VHDL ����֮��(n��i)������������C��ʹ����������Ҫ����������)

��(d��ng)VHDL�c�挍(sh��)��Ӳ�����P(gu��n)�ĕr(sh��)��(bi��o)��(zh��n) 1076.3( �r(sh��)���J(r��n)�锵(sh��)ֵ�Ę�(bi��o)��(zh��n)��C���ǘ�(bi��o)��(zh��n)) �� VHDL ��(sh��)��(j��)��Ͷ��x��(bi��o)��(zh��n)�˳������ጡ��@һ��(g��)�� 1995 �ױ��l(f��)���Ę�(bi��o)��(zh��n)�A(y��)Ӌ(j��)�����S����(x��)�T ( �ǘ�(bi��o)��(zh��n)��) ���b�C�Ϲ��ߵďS���ѽ�(j��ng)�a(ch��n)�����ґ�(y��ng)�õĮa(ch��n)Ʒ��

IEEE�� 1076.3��(bi��o)��(zh��n)��ʹ��IEEE 1164�C��ģ�Mʹ������ʲô�� ���Ә�(bi��o)��(zh��n) 1076 �Ĺ���, ����(qi��ng)�ڲ�ͬ�ďS��֮�g�ļ����ԡ���(bi��o)��(zh��n)�� 1076.3 ����, ������������֮�У�

1)��(bi��o)��(zh��n)�ăr(ji��)ֵ���C����Ӳ����ጌ���IEEE ��(bi��o)��(zh��n)��1076, �Bͬ�� IEEE ���x�� std_ulogic ��͵Ľ�ጶ��x�� boolean ���1164��

2) һ��?zh��)ṩ��std_ulogic����A(ch��)��ͨ���C���@���C�������eʹ�õ�, ��?y��n)����r(sh��)�����Ў����ăr(ji��)ֵ���_(d��)߉��

3)���(bi��o)��(zh��n)�Ķ��x�����Ҳ��������g(sh��)��(sh��)��(j��)��ͣ��Bͬ���g(sh��)��׃��������D(zhu��n)׃�Є�һ��������Щ��͡�

�r(sh��)�g���Ŕ�(sh��)��(j��)��ע�⌦һ��(g��)ģ�Mģ����һ��(g��)���_��(sh��)��(j��)����Ҫ����ģ�M��VHDL 1076 ��(bi��o)��(zh��n)������N�Z��������r(sh��)�g����ע���������Ȼ���������ڕr(sh��)�g����ģ�ͱ������ⲿ���_(d��)�r(sh��)�g���Ŕ�(sh��)��(j��)������һ��(g��)��(bi��o)��(zh��n)�ķ�����

�^(q��)��ģ�Mģ�͵Ą��������͕r(sh��)�g����Ҏ(gu��)����������S����������Ҫ�ġ�Verilog ���ܶ�( VHDL�s����Č���) ����Ҫ����֮һ��Verilog ���ܶȞ�r(sh��)�g����ע�����_�ذ���һ��(g��)������Ҫ����(sh��)���@һ��(g��)��������(bi��o)��(zh��n)�����t��ʽ���� SDF, ���S�r(sh��)�g���Ŕ�(sh��)��(j��)��һ�N�Ƴɱ�����ʽ�б����_(d��)������ģ�M�ĕr(sh��)���M(j��n)�� Verilog �r(sh��)�g����ģ��֮��(n��i)��

IEEE 1076.4 ��(bi��o)��(zh��n), ��1995��������IEEE ����,���@һ��(g��)��������һ��(g��)��(bi��o)��(zh��n)�ij������VHDL���@��(g��)��(bi��o)��(zh��n)��Ŭ�� (��������Ҫ��, ��VHDL ��ASIC�D���^������) �����һ�N��Ҫ�Ą����� ASIC�S�̺�����ʹ��׃�ɸ����a(ch��n)���r(sh��)�g����ģ���m����VHDL ��Verilog���ܶ�оƬ����?y��n)��@һ��(g��)����, IEEE 1076.4 ��Verilog �sSDF �������攵(sh��)��(j��)��ʽ�ஔ(d��ng)���ơ�

�㑪(y��ng)ԓʹ�� VHDL?

��ʲô�x��ʹ�� VHDL ��������O(sh��)Ӌ(j��)? ���S���п��ܵ����ɡ�����㆖�����(sh��)�� VHDL���ߏS���@һ��(g��)���}���㌢���õĵ�һ��(g��)���ǡ��YӍ�Ƽ���������������a(ch��n)������ ���Ǿ����@���^ʲô�أ� ��������ڴ�������˿��ٵ�ʹ�� VHDL �����O(sh��)Ӌ(j��)�����^ʹ����ĬF(xi��n)���O(sh��)Ӌ(j��)������

���ǵĿ϶�,���ǻ��S������ʹ������һĿ�ģ�����ֻ�Ю�(d��ng)������ԽY(ji��)��(g��u)�����ӑ�(y��ng)�� VHDL����(d��ng)��ʹ�ýY(ji��)��(g��u)�������϶��µķ�ʽ�O(sh��)Ӌ(j��)�ĕr(sh��)��VHDL( ��һ�N�Y(ji��)��(g��u)��ܛ���O(sh��)Ӌ(j��)�Z��) ��������ġ����a(ch��n)�������������Ժ��ܵ���Ӱ푣���(d��ng)���ѽ�(j��ng)�� VHDL�ϸ��ߵ��ʵnjW(xu��)��(x��)���������ѽ�(j��ng)�۷eһ�g�����ٶ�ʹ�� VHDL �ɷݵĈD���^�ĕr(sh��)��

��(d��ng)���_ʼʹ��VHDL ������a(ch��n)���ĕr(sh��)�����a(ch��n)������Ҳ�����l(f��)�����(du��)�ɆT֮�g�Ĝ�ͨ���Ү�(d��ng)���ģ�M���O(sh��)Ӌ(j��)�ɵõĴ_�J(r��n)���ñ��^�����Ĺ��ߕr(sh��)����֮�⣬ VHDL���S����һ��(g��)�^��ij���ˮƽ�O(sh��)Ӌ(j��)����������ļ������T�����䌍(sh��)���������O(sh��)Ӌ(j��)�Ą������ܰl(f��)�����f��

VHDL�����������������a(ch��n)��? ��VHDL��������ʹ�ÈD���^��(sh��)��(j��)�������ձ�ġ�VHDL�M��ʹ�O(sh��)Ӌ(j��)�؏�(f��)ʹ�����X����Ȼ��������l(f��)�F(xi��n)�����ٶ�ʹ���ܴa�����棬�㌢���ܿ������Լ�����˼��ʹ�����ɞ�һ����;�ķ������㌦VHDL �����������ʽ���ܴa����׃��һ��(g��)�Ԅӵķ��䡣

ʹ�� VHDL ��������Ҫ������������O(sh��)Ӌ(j��)�Ԅӻ� (EDA) �Ĺ��ߺ���Ŀ��(bi��o)���g(sh��)����İl(f��)չ�ٶȺܿ졣ʹ��һ�N��(bi��o)��(zh��n)���Z�ԣ����� VHDL ����Ч������o�����M(j��n)����ľ�·�����ĸ����M(j��n)�Ĺ��� ( �e�����f����һ��(g��)���������r(ji��)ģ�M����һ��(g��)�����M(j��n)��) �C(j��)����Ҳ�ٌ���(zh��n)���b��Ŀ��(bi��o) ( �e�����fASICs �� FPGAs �ͺϳ��� PLDs) ������͵ľ�·������������ʹ�Ø�(bi��o)��(zh��n)���O(sh��)Ӌ(j��)�M(j��n)�뷽��������

VHDL�r(sh��)���·�O(sh��)Ӌ(j��)������

VHDL�Ĵ������Ǟ���֧�֕r(sh��)���·���O(sh��)Ӌ(j��)�ģ��e�أ������M(j��n)�̡����҂��ѽ�(j��ng)��4.7��(ji��)���B�^�ˣ��҂�߀���ڵ����µ�VHDL�����������������ֽ�BһЩ�������������o��һЩ������õ����ӡ�����ø�ȫ������ӌ��ڵڰ��µ�VHDL���ֽo����

�����r(sh��)���·:

һ��(g��)VHDL�M(j��n)�̺�ۙ��̖׃����ģ�M�¼��б�C(j��)�Ƙ�(g��u)������VHDL��̎�������r(sh��)���·�Ļ��A(ch��)���e���ˣ������r(sh��)���·���S��ݔ����̖��׃���a(ch��n)��׃�������@Щ��B(t��i)��׃����һ��(g��)�����h(hu��n)���à�B(t��i)�D�@ʾ���������Ƿ����h(hu��n)��(w��n)��������ģ�M�У��@�������¼��б��е�ģ�Mݔ����̖��׃�����@ʾ�����ң��A(y��)�����M(j��n)�̕��ڦĕr(sh��)�g�κأ����҂����@Щ׃��ֱ��������׃����̖���F(xi��n)��

��7-36����һ��(g��)��VHDL�Z�Ծ�����S-R�i�����ij�����Y(ji��)��(g��u)�w�����ɂ�(g��)���l(f��)�Z�䣬ÿһ�䶼�������l(f��)һ��(g��)�M(j��n)�̣���ͬ��4.7.9�NӑՓ��һ�ӡ��@Щ�M(j��n)�̻���خa(ch��n)��һ��(g��)���ε�S-R�i�����Ĺ����О顣

VHDL����������挍(sh��)��̎����(d��ng)S-Rͬ�r(sh��)׃������r�����кܶ����Ȥ�ķ���Y(ji��)���ڬF(xi��n)�ڷ����^���У�ֻҪ��ͬ�r(sh��)����S��R���ؑ���536��ϵĈD������һ��(g��)������S-R�i��������������r��������ʎ���M(j��n)�벻�ɜy��B(t��i)���@��(g��)��B(t��i)�����������õ��i����ÿ��(g��)�Z��Ĉ�(zh��)�Ќ���������һ��(g��)�Z��Ĉ�(zh��)�У���(j��ng)�^һЩ�؏�(f��)��һ��(g��)�O(sh��)Ӌ(j��)�÷dz��õķ������͌��@ʾ���}�����ڷ���r(sh��)�g����r(sh��)�������t�������ȡ�����ֹͣ���档

����������7-36���@ʾ��S-R�i������S��Rͬ�r(sh��)��(f��)λ�r(sh��)���a(ch��n)��һ��(g��)��U��ݔ���ƺ��ܺã�����(sh��)�ϲ���һ���������e���ˣ���һ��(g��)VHDL�ľ����߶��ԣ��Z�������(qi��ng)��ģ����������p�ɵ�����һ��(g��)�߂�ij�О��ģ�ͣ��@��(g��)ģ�͌�����VHDL�ĕr(sh��)�gģ�ͣ��@�����҂�߀�]��̽ӑ����ݔ��׃��̫�����r�£�߀δ��������ģ�͵ď�(f��)λ�r(sh��)�g�ͮa(ch��n)����U��ݔ���M(j��n)��ģ�M��

ӛס�����һ��(g��)�·�п����M(j��n)�벻����B(t��i)���Ͳ��ܱ��C�������ܙz�y�����������ڴ��͵��O(sh��)Ӌ(j��)�У�һ��(g��)ϵ�y(t��ng)���O(sh��)Ӌ(j��)��õر��ⲻ���B(t��i)�ķ�ʽ���м�(x��)���J(r��n)�����o(h��)���IJ�ͬ��߅�أ�����ͬ��8.9����ӑՓ���ǘӡ�

��7-37

****��U����Ҫʲô****

7��12��2 �r(sh��)��·

�ڌ�(sh��)�H�O(sh��)Ӌ(j��)�r(sh��)����VHDL�Z���M(j��n)��ģ�M�Ĵ����(sh��)��(sh��)���O(sh��)Ӌ(j��)�Ǖr(sh��)��ġ���߅���|�l(f��)����ͬ��ϵ�y(t��ng)�������҂����W(xu��)��VHDL������߀��һ��(g��)������Ҫ����߅���|�l(f��)�����О飬�����¼����ԡ����Ա��B�ӵ�һ��(g��)��̖�����a(ch��n)��һ�N��������(sh��)ֵ�������̖���l(f��)���¼�������һ��(g��)�M(j��n)��ȥ��(zh��)�Ю�(d��ng)ǰ��ģ�Mѭ�h(hu��n)����ô�͌��ˣ���t�������e(cu��)�`�ġ�

�á��¼����ԡ����҂���ģ�Mһ��(g��)�ӑB(t��i)߅��D�|�l(f��)�����О飬��ͬ�ڱ�7-37���������ǘӡ�

�@�ͬ������CLR�ȕr(sh��)��·�������κ��О鶼��(y��u)�ȣ�������O(sh��)Ӌ(j��)�Z��r(sh��)�����ȱ��z�y������M��IF�l������ô�͙z�yELSIF�Z�䣬��CLK��߅�ؕr(sh��)����B(t��i)�Z�䌢����(zh��)�У�ӛס����CLK��EVENT����CLK���κ�׃���������ã�����CLK=1����ʾֻ��CLK�����ز������ã�߀��һЩ������ʽ�혋(g��u)�������|�l(f��)���О���M(j��n)�̺͠�B(t��i)����7-38�@ʾ�˃ɷN��ʽ������һ��(g��)D�|�l(f��)�����]��CLRݔ�룩��

��7-38

��һ��(g��)�r(sh��)��·�Ĝyԇƽ�_��һ������Ҫ�������Ǯa(ch��n)��һ��(g��)ϵ�y(t��ng)�r(sh��)���̖���@�����p�ɵ���ɣ���������һ��(g��)�M(j��n)������һ��(g��)ѭ�h(hu��n)���D��7-39��ʾ�����һ��(g��)100MHz�Ķ�����60%����ֵ��ѭ�h(hu��n)�r(sh��)���̖��

�C�Ϲ���

�������֪��һ��(g��)������������Ό�(sh��)�F(xi��n)����7-37���7-38�е�߅���|�l(f��)���О�׃��һ��(g��)��Ч���|�l(f��)���О�ģ������(sh��)���߃H���R���S��(w��n)���������|�l(f��)�О�ķ�ʽ������������?q��)����g(sh��)�а���������һ��(g��)�|�l(f��)��Ԫ����

��XILINX����ϵ��1��5�汾ܛ���еľC�Ϸ��������ܱ��R��CLK��EVENT���͡�CLK=1����������Ҳ�����҂������������ġ����˽o��������VHDL���S�ͬ�ķ�ʽ����ͬһ��(g��)���ܣ����ڱ�7-38����ʾ����VHDL�x��ָ�ϡ�������Peter ashden(morgan kanfmann,1996)�����^�@Щ��(n��i)�ݣ���ͨ�^ijЩ�ģ��ڲ�ͬ�Ĺ������\(y��n)���^���H�Hһ�N�ܾC���ķN��ʽ�е����N�������(sh��)ֻ��̎��ɂ�(g��)����ˣ�����Ҫȥ�W(xu��)��(x��)�����ù����m�ϵ�����������

������

��7-39

�����F(xi��n)���L�ڴ��ڣ����Һܾ���ǰ���С���ϣ�D�܌W(xu��)�҂��ڎ�ǧ��ǰ�������^�����F(xi��n)��һЩ�F(xi��n)���܌W(xu��)�����������^�������ԵĘ�(bi��o)�}�зQDevo sang�鲻���F(xi��n)����������������Ȼ���ܛQ�����ȥ���������ȫ��

���i������IBM�����·�O(sh��)Ӌ(j��)��Ҫע�ص��ǒ��蹦�ܣ������|�l(f��)���������AJ.Mc����˹����FPGA���O(sh��)Ӌ(j��)�������@���������r(sh��)���·��͡�Ȼ����߀���������Ҳ����(y��ng)���������fʽ�ķ��x���O(sh��)Ӌ(j��)�У������ȫ�ص���չ�߉�r(sh��)����ͬ�ӣ��ڬF(xi��n)���Ă��y(t��ng)VLSI�O(sh��)Ӌ(j��)��Ҳ�õ����e��(g��)���ӣ�ͬ���r(sh��)���B(t��i)�C(j��)��ͨ���ĎN�}�_ģʽ�·��һ��(g��)�������ӡ��@�N�·����һ��(g��)�����(g��)�}�_ݔ�룬��ij��(g��)�r(sh��)��ֻ��һ��(g��)�}�_����һ��(g��)�}�_�ڶ���(sh��)��B(t��i)׃���r(sh��)�a(ch��n)����H�H���}�_�Ůa(ch��n)����B(t��i)׃����(d��ng)һ��(g��)�}�_�a(ch��n)���r(sh��)�����}�_ݔ���Ƿ�(w��n)���ġ���ͬ���r(sh��)�S��B(t��i)�C(j��)�У�һ��(g��)�}�_��ָһ��(g��)�r(sh��)犵��|�l(f��)߅�أ�Ȼ���ö��}�_ݔ��Ҳ�����O(sh��)Ӌ(j��)�·�����H����ͨ��߅���|�l(f��)�������ô惦��Ԫ��Ҳ���O(sh��)Ӌ(j��)���@Щ��������Mc����˹�˵ġ�߉�O(sh��)Ӌ(j��)ԭ�������кܺõ�������

һ�N�}�_�·���e��Ҫ�������Mc����˹�˵ĕ���Ҳ��ӑՓ�����������Ƕ����i��C(j��)��һ�N��VLSI�п��еĶ����i�淽ʽ�ڿ����º͌������������ĕ���VLSIϵ�y(t��ng)��(d��o)Փ����1980�꣬�۵���-��˹������磩��ӑՓ�^��

�@Щ��B(t��i)�C(j��)�����Ϝp������߅���|�l(f��)���еĝ���Σ�U(xi��n)����ʽ����һ�������دB�r(sh��)犵���ʹ�ܶ˵��i�����팍(sh��)�F(xi��n)��

�ڸ�߉�ǽ̲���ӑՓ�^���I(y��)��댣�I(y��)�Ġ�B(t��i)�D�Ļ�������������Mc����˹��1986�ꌑ�ĕ�������Ĕ�(sh��)�W(xu��)�ϵ��P(gu��n)���@Щ��ʽ��ӑՓ�������r(sh��)��C(j��)����Փ�ϵ��^�c(di��n)�ڡ��_�P(gu��n)�D(zhu��n)�Q�������Ԅӻ���Փ����1978���ڶ��棩�����^��������ͬ�ڱ�����ӑՓ�ģ��������Ġ�B(t��i)�D���a(ch��n)��һ��(g��)ģ���ĴΑB(t��i)�О����������IF-THEN-ELSE����VHDL�еĽY(ji��)��(g��u)����ABEL��VHDL�ܜp���@�Nģ����������������������@�΄�(w��)�ġ�����(sh��)�֠�B(t��i)�C(j��)����ASM����(bi��o)ע��һ�N�c��IF-THEN-ELSE����ͬ�����Dʽ��������������25��ǰ�ͳ��F(xi��n)�^����ˣ�ASM�D��Hewlett-Packard��(sh��)�(y��n)�ұ������_�l(f��)���l(f��)���������R˹•E•�W�����^���ɊW���Ĵ�W(xu��)ͬ�W(xu��)����˹�ط�R�������ĕ����à�B(t��i)�C(j��)�O(sh��)Ӌ(j��)߉ϵ�y(t��ng)���б�����ذl(f��)չ�ˡ�

��ASM�D�O(sh��)Ӌ(j��)�;C�ϵķ����ܿ��ڸ��N�̲��г��F(xi��n)������F.P�����_��D.E�S�ˠ��ĕ�����(sh��)���O(sh��)Ӌ(j��)ˇ�g(sh��)����M.Ī��˹�R��¡���(sh��)���O(sh��)Ӌ(j��)����ͬ�����������x�ĕ���ǰ�ɰ���Ҳ�����ˡ�

����һ��(g��)��Ҫ�f�����P(gu��n)��������B(t��i)�C(j��)���ǂ��y(t��ng)��B(t��i)�D�ĔU(ku��)չ�����Q��MDS�D����������.I.�������ڕ�����(sh��)���O(sh��)Ӌ(j��)�Ĺ��̷������аl(f��)����ASM�D��MDS�D�F(xi��n)�ڽ^�ֱ�HDL�Z�Ժ������ľ��g�����档

�S����(sh��)���O(sh��)Ӌ(j��)�m�ϸ��NCAD�h(hu��n)���������·�D�O(sh��)Ӌ(j��)���ߣ����ҵ��ǣ��@Щ�h(hu��n)��ֻ֧�ւ��y(t��ng)�Ġ�B(t��i)�D����һ��(g��)�O(sh��)Ӌ(j��)�ߺ������O(sh��)Ӌ(j��)һ��(g��)�a(ch��n)���ΑB(t��i)ģ���О���O(sh��)Ӌ(j��)����ˣ��҂�(g��)�˽��h�ǣ�������h(yu��n)�x��B(t��i)�D�O(sh��)Ӌ(j��)����(ji��n)����HDL���O(sh��)Ӌ(j��)��Ġ�B(t��i)�C(j��)��

�҂��@�����^ͬ���r(sh��)���c��B(t��i)�C(j��)�yԇʸ���Y(ji��)�ϵ���Ҫ�ԣ��_��(sh��)����һ�N�P(gu��n)��ͬ���r(sh��)��İl(f��)չ����䵫�֎�����ӛ����Փ�͌�(sh��)�`�������d�ڡ���ͥ��(sh��)�(y��n)�ҡ����@�����������C�����ڕ���߉�C(j��)�����ޠ�B(t��i)ģʽ����1968����棩���v���^��

��������ĕ��������@����(j��ng)��ĕ�������֪�������������ՈҪӛס�����O(sh��)Ӌ(j��)��ÿ��(g��)��B(t��i)�C(j��)��ݔ��˼�һ��(g��)��(f��)λݔ�롣

�� �x

������Ҫ���xָ��(d��o)�ҵ��Z���o�ώ������ҵ��n�}�O(sh��)Ӌ(j��)��Փ�������g�����o����Ϥ�ĵ�ָ��(d��o)�����x�}�������ă�(y��u)�x��ܛӲ���Č�(sh��)�F(xi��n)���棬�Z�ώ����H�o���ˌ��F����Ҋ�������M(j��n)�������ĵĆ��ϣ��@�Ӳ����_����ҵ�ҕҰ��߀��l(f��)���ҵķe�O�ԡ�ͬ�r(sh��)���Z�ώ��ΌW(xu��)��(y��n)֔(j��n)�������������t�ͣ��o�Ҙ��������ˡ��ΌW(xu��)�İ�ӣ����ҽ��ČW(xu��)��(x��)���������a(ch��n)���L�ڵ�Ӱ푡��ڴˣ�֔(j��n)���Z�ώ��������\�����x�⣡

ͬ�r(sh��)߀Ҫ���x��(sh��)�(y��n)�ҵ������ώ�����V�x�ώ������ώ��ȣ������������O(sh��)Ӌ(j��)���g�o���˟o˽�Ď�����ָ��(d��o)��

ͬ�r(sh��)߀Ҫ���x�����^�ҵ�ͬ�W(xu��)�����ڱ���Փ���n�}�Č�(sh��)�(y��n)�^���У��õ��ˏ��A�ġ������F�������ͬ�W(xu��)�Ď��������@����������ʾ������x�⣡

����߀Ҫ���x�����P(gu��n)�ĺ͎����^�ҵ����т���

| �gӭ���R (http://m.raoushi.com/bbs/) |

Powered by Discuz! X3.1 |

MAX+PLUSII File NEW Text Editor File/.gdf /.scf ݔ����� ���桢���g �{(di��o)ԇ���� ���g�����桢�\(y��n)�� �{(di��o)ԇ��ɺ��ò������d�����d������CPLDоƬ ��ɟ�������Ӳ���·���{(di��o)ԇ �ġ��{(di��o)ԇ���� ����O(sh��)Ӌ(j��)��

MAX+PLUSII File NEW Text Editor File/.gdf /.scf ݔ����� ���桢���g �{(di��o)ԇ���� ���g�����桢�\(y��n)�� �{(di��o)ԇ��ɺ��ò������d�����d������CPLDоƬ ��ɟ�������Ӳ���·���{(di��o)ԇ �ġ��{(di��o)ԇ���� ����O(sh��)Ӌ(j��)��