[組合邏輯]

源程序:可以認為 led_test 就是一個芯片

module led_test(a, b, c, out);

input a; // 輸入信號 input b; // 輸入信號 input c; // 輸入信號

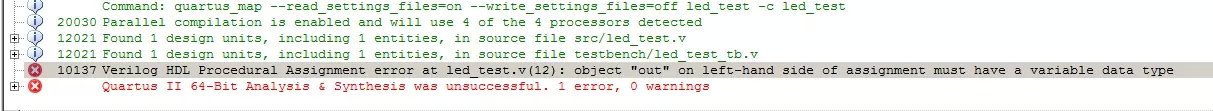

//output [7:0]out; // 由于要用到 always 程序塊中,需要聲明為 reg 類型 // 如果不是 reg 類型則會報錯 // Error (10137): Verilog HDL Procedural Assignment error at led_test.v(12): // object "out" on left-hand side of assignment must have a variable data type output reg [7:0]out; // 輸出信號

always@(a, b, c)begin case({a, b, c}) 3'b000 : out = 8'b0000_0001; 3'b001 : out = 8'b0000_0010; 3'b010 : out = 8'b0000_0100; 3'b011 : out = 8'b0000_1000; 3'b100 : out = 8'b0001_0000; 3'b101 : out = 8'b0010_0000; 3'b110 : out = 8'b0100_0000; 3'b111 : out = 8'b1000_0000; endcase end

endmodule

|

仿真程序:

`timescale 1ns/1ns // 延時時間單位/仿真精度 module led_test_tb;

reg a, b, c; wire[7:0] out;

led_test u1(.a(a), .b(b), .c(c), .out(out)); // 將端口(IO口)連接到 led_test 芯片中

initial begin

a = 0; b = 0; c = 0; // 設置端口(IO口)的電平狀態 #200; a = 0; b = 0; c = 1; #200; a = 0; b = 1; c = 0; #200; a = 0; b = 1; c = 1; #200; a = 1; b = 0; c = 0; #200; a = 1; b = 0; c = 1; #200; a = 1; b = 1; c = 0; #200; a = 1; b = 1; c = 1; #200; $stop; // 停止執行

end

endmodule

|

知識點總結:

1、always 里面的變量必須是 reg 類型,否則會報如下錯誤

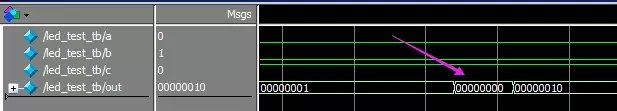

2、從仿真的角度來看,out 輸出的電平并不是理想的。

2、從仿真的角度來看,out 輸出的電平并不是理想的。

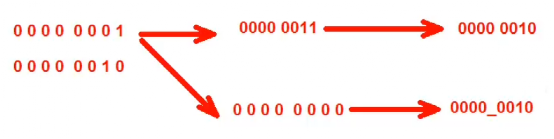

放大其中,從 00000001 跳變到 00000010 中間還有一個 00000000

從 00000001 變化到 0000010 有兩個bit會發生變化,由于電路結構關系,它們有可能不會同時變化,有可能bit1最開始變化,也有可能bit0最開始變化。

還有另外一種情況:

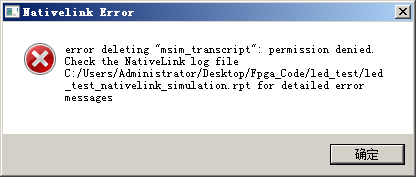

3、如果已經運行了仿真程序,則會報如下錯誤

作業:實現一個4-16 譯碼器

源程序:

/* 4-16 譯碼器 */ module led_test(a, b, c, d, out);

input a, b, c, d; output reg[15:0] out;

always@(a, b, c, d)begin

case({a, b, c, d}) 4'b0000 : out = 16'b0000_0000_0000_0001; 4'b0001 : out = 16'b0000_0000_0000_0010; 4'b0010 : out = 16'b0000_0000_0000_0100; 4'b0011 : out = 16'b0000_0000_0000_1000; 4'b0100 : out = 16'b0000_0000_0001_0000; 4'b0101 : out = 16'b0000_0000_0010_0000; 4'b0110 : out = 16'b0000_0000_0100_0000; 4'b0111 : out = 16'b0000_0000_1000_0000; 4'b1000 : out = 16'b0000_0001_0000_0000; 4'b1001 : out = 16'b0000_0010_0000_0000; 4'b1010 : out = 16'b0000_0100_0000_0000; 4'b1011 : out = 16'b0000_1000_0000_0000; 4'b1100 : out = 16'b0001_0000_0000_0000; 4'b1101 : out = 16'b0010_0000_0000_0000; 4'b1110 : out = 16'b0100_0000_0000_0000; 4'b1111 : out = 16'b1000_0000_0000_0000; endcase

end

endmodule

|

仿真程序:

`timescale 1ns/1ns module led_test_tb;

reg a, b, c, d; wire[15:0] out;

led_test u1(.a(a), .b(b), .c(c), .d(d), .out(out));

initial begin a = 0; b = 0; c = 0; d = 0; #200; a = 0; b = 0; c = 0; d = 1; #200; a = 0; b = 0; c = 1; d = 0; #200; a = 0; b = 0; c = 1; d = 1; #200; a = 0; b = 1; c = 0; d = 0; #200; a = 0; b = 1; c = 0; d = 1; #200; a = 0; b = 1; c = 1; d = 0; #200; a = 0; b = 1; c = 1; d = 1; #200; a = 1; b = 0; c = 0; d = 0; #200; a = 1; b = 0; c = 0; d = 1; #200; a = 1; b = 0; c = 1; d = 0; #200; a = 1; b = 0; c = 1; d = 1; #200; a = 1; b = 1; c = 0; d = 0; #200; a = 1; b = 1; c = 0; d = 1; #200; a = 1; b = 1; c = 1; d = 0; #200; a = 1; b = 1; c = 1; d = 1; #200; $stop; end endmodule

|

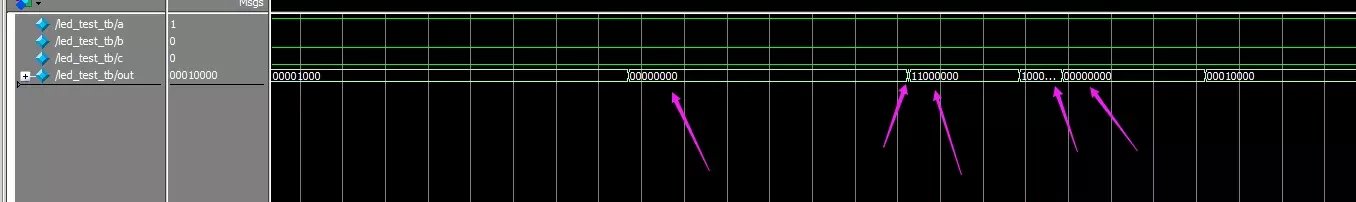

仿真波形: