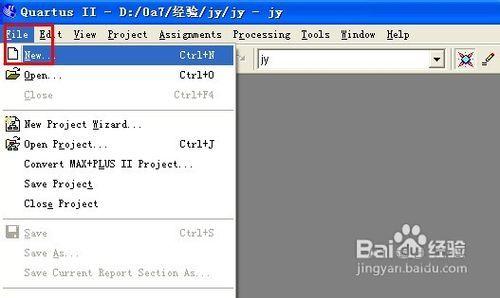

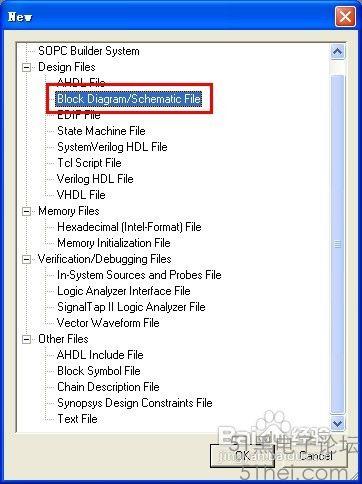

�@���҂�Ĭ�J(r��n)���ѽ�(j��ng)�½����˹��̣��ڡ�File���ˆ����c(di��n)����New�����������Ñ��O(sh��)Ӌ(j��)������?q��)����ڡ�New�����x��Design Files��-��Block Diagram/Schematic File��ԭ��D�ļ�ݔ��

���E��x

���E��x

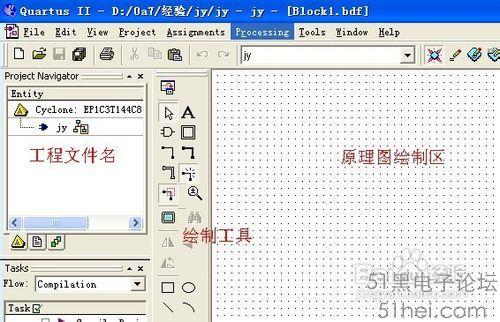

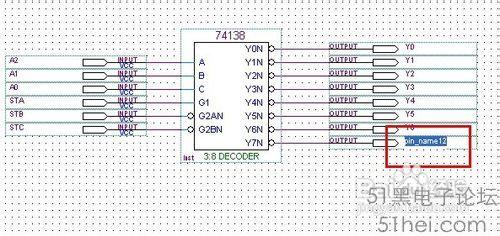

����ԭ��D�O(sh��)Ӌ(j��)�ļ�

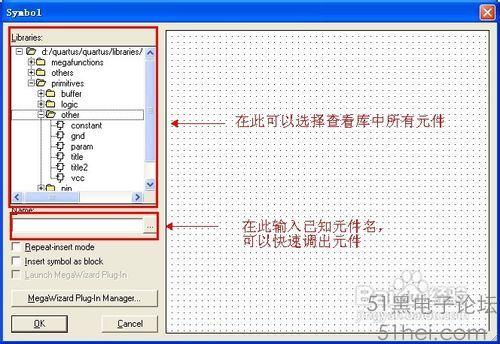

�{(di��o)�Å���(sh��)��Ԫ�������L�D�^(q��)�p�����(bi��o)���I�����������ӷ�̖(h��o)Ԫ���Ĵ���

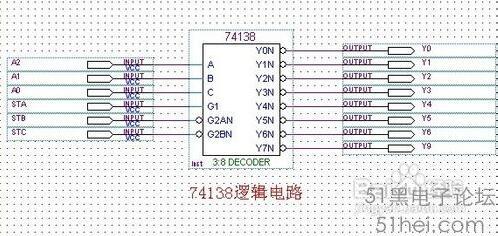

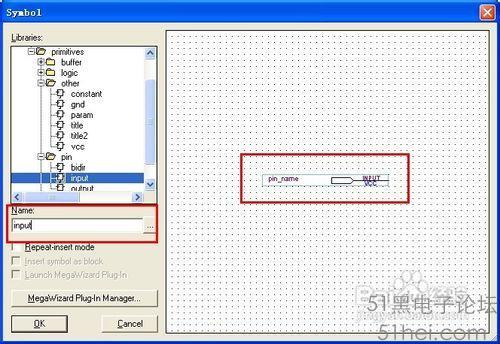

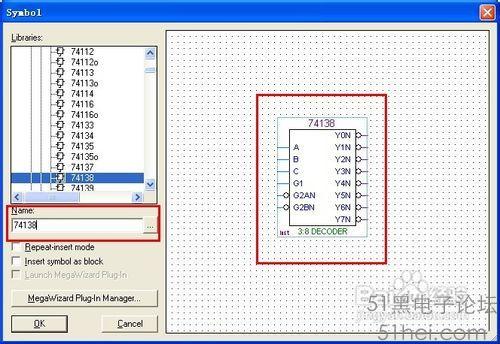

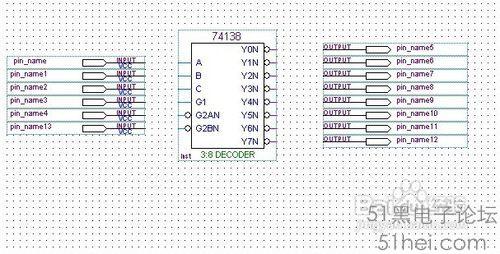

�քe�{(di��o)��ݔ��˿ڡ�input����߉������74138��

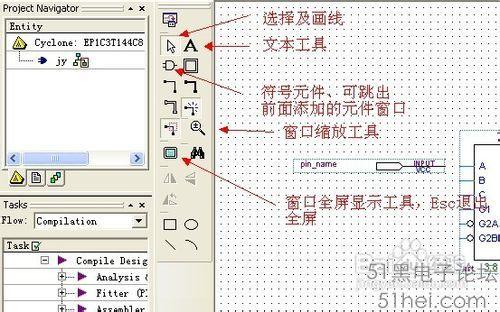

�L�D���Ʋ�����ʹ�ÿs�Ź��߰��o��Ո(q��ng)�ГQ�ذ��o���x�������ߣ������܌�(du��)�L�D�M(j��n)�о���

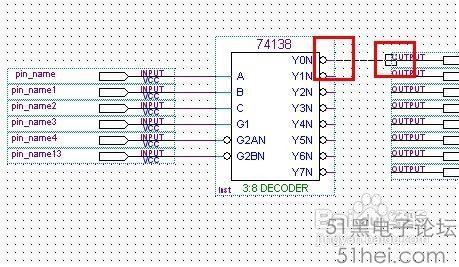

�ķ�̖(h��o)��(k��)���{(di��o)����Ҫ��ݔ�롢ݔ���˿ڣ��ŷ����R

��ɮ����B�Ӳ��������(bi��o)�ŵ����c(di��n)̎����(hu��)�Ԅ�(d��ng)�����������I�τ�(d��ng)��Ŀ��(bi��o)̎��ጷź����һ�ή���������

���(bi��o)���I�p���˿�������Dʾ74138�·Y7N����ʾ��ֱ��ݔ���Ñ��Զ��x�����ּ��ɡ�74138߉�y(c��)ԇ�·ԭ��D�O(sh��)Ӌ(j��)�ꮅ��

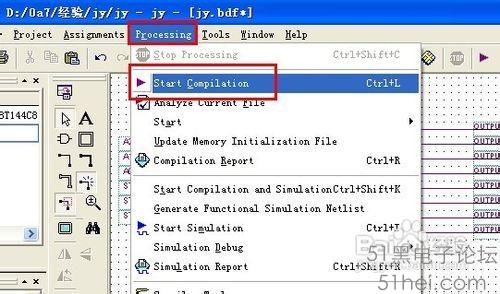

�������ˆΡ�Processing�����x��Start Compilation��������(d��ng)ȫ�̾��g

ȫ�̾��g������(b��o)�棺

�x��Processing/Start Compilation,�Ԅ�(d��ng)��ɷ��������e(cu��)���C�ϡ��m�䡢�R�����r(sh��)�������ȫ�^(gu��)�̡�

���g�^(gu��)���У��e(cu��)�`��Ϣͨ�^(gu��)�·�����Ϣ��ָʾ���tɫ���w�����p������Ϣ�����Զ�λ���e(cu��)�`����̎���������ڴ��M(j��n)�о��gֱ���ų������e(cu��)�`��

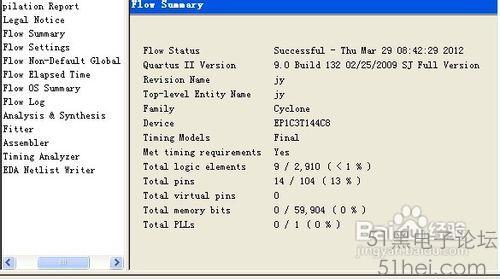

���g�ɹ���(hu��)�������g��(b��o)�棬�@ʾ���P(gu��n)���g��Ϣ��

QuartusII�ľ��g����һϵ��̎��ģ�K��(g��u)�ɣ��@Щģ�Kؓ(f��)؟(z��)��(du��)�O(sh��)Ӌ(j��)�(xi��ng)Ŀ�ęz�e(cu��)��߉�C�ϡ��Y(ji��)��(g��u)�C�ϡ�ݔ���Y(ji��)���ľ����ã��Լ��r(sh��)�������

���@һ�^(gu��)���У����O(sh��)Ӌ(j��)�(xi��ng)Ŀ�m�䵽FPGA/CPLDĿ��(bi��o)�����У�ͬ�r(sh��)�a(ch��n)������;��ݔ���ļ����繦�͕ܺr(sh��)����Ϣ�ļ����������̵�Ŀ��(bi��o)�ļ���

���g�����șz��������O(sh��)Ӌ(j��)�ļ��п��ܵ��e(cu��)�`��Ϣ���Թ��O(sh��)Ӌ(j��)���ų���Ȼ��a(ch��n)��һ��(g��)�Y(ji��)��(g��u)���ľW(w��ng)���ļ����_(d��)���·ԭ��D�ļ���

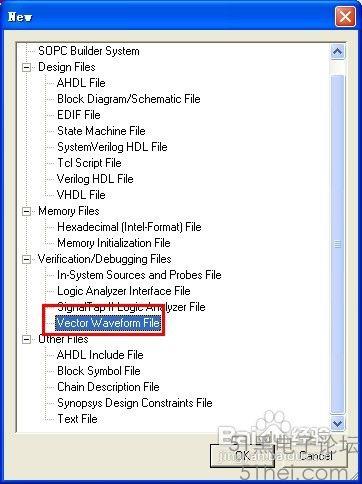

���̾��g��ɺ��O(sh��)Ӌ(j��)�Y(ji��)���Ƿ�M���O(sh��)Ӌ(j��)Ҫ����ͨ�^(gu��)�r(sh��)������(l��i)��������������ʸ���ļ�

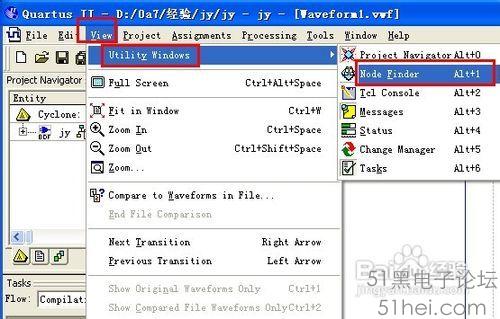

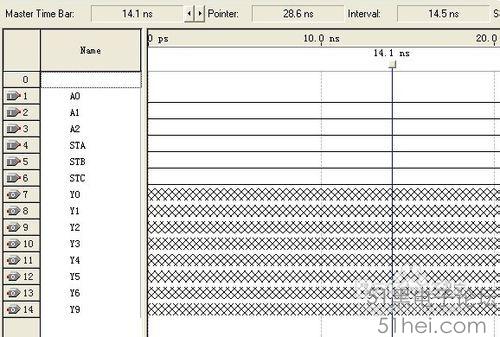

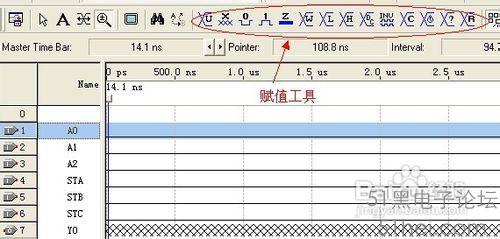

�������_��(ji��)�c(di��n)���x��ˆΡ�View��-��Utility Windows��-��Node Finder������

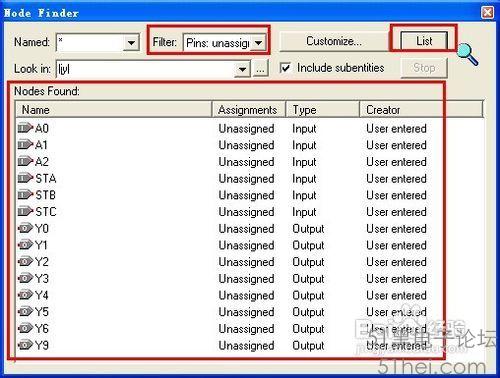

��Filter���x��Pins��unassigned�����نΓ���List�����г����_�˿�

��Nodes Found�·����б����x�����г��Ķ˿ڣ������Ϸŵ������ļ������_���^(q��)

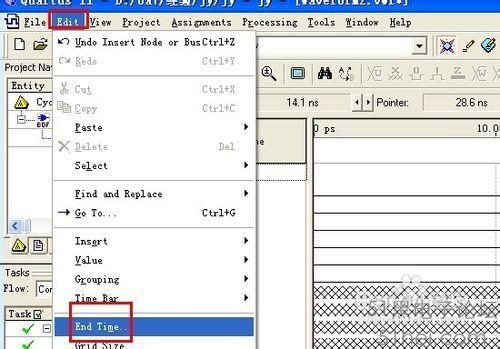

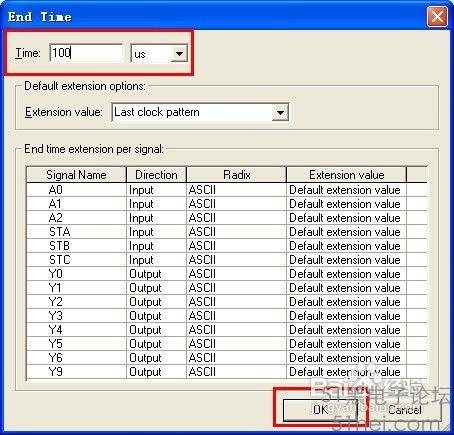

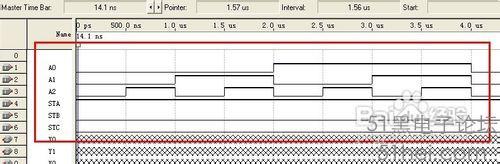

�O(sh��)�÷���r(sh��)�g�L(zh��ng)�����x��ˆΡ�Edit��-��End Time�����Ĭ�J(r��n)��1us���@����O(sh��)�Þ�100us

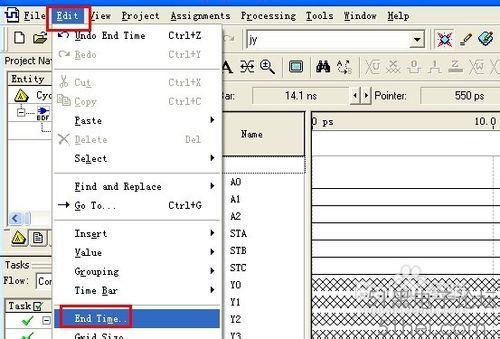

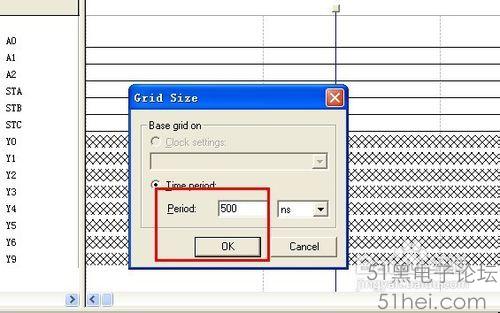

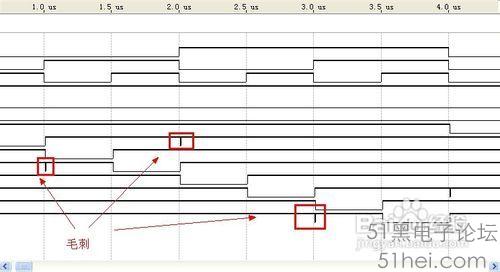

�O(sh��)�÷���r(sh��)�g�������x��ˆΡ�Edit��-��Grid Size�������Ĭ�J(r��n)��10ns�����ڸ�(j��ng)��(zh��ng)ð�U(xi��n)�Ĵ��ڣ��ڷ���r(sh��)��̖(h��o)���κʹ���ë�̻�B��һ��Ӱ푷���Y(ji��)������ˣ��@���O(sh��)�Þ�500ns

��ݔ��˿���̖(h��o)��ʹ�ô��ڿs�ţ����I�Ŵ����I�sС���Ѳ��οs�ŵ����m�̶�

����(d��ng)�r(sh��)����棬�������ˆΡ�Processing�����x��Start Simulation�����������ο�Ҋ(ji��n)���c74LS138������ֵ��һ�£��Y(ji��)�����_

END