| |

| |

|

| |

<strike id="39dxl"><nav id="39dxl"></nav></strike>

作者: 一博科技 時間: 2025-12-10 10:29

標(biāo)題: EXCUSE ME,表層的AC耦合電容和PCB內(nèi)層的高速線會有串?dāng)_?

高速先生成員-- 黃剛

這到底是在描述一種什么樣的設(shè)計場景呢?其實是我們在高速設(shè)計中一個很典型的case。一般來說,芯片到芯片的高速鏈路中間都會有AC耦合電容,作用說了500多次了,這里就不重復(fù)了哈。由于AC耦合電容一般會放在靠近接收端,剛好在這個區(qū)域會和另外一個方向來的高速信號進行匯集,所以我們經(jīng)常會看到下面這樣的電容和高速走線交匯的設(shè)計。

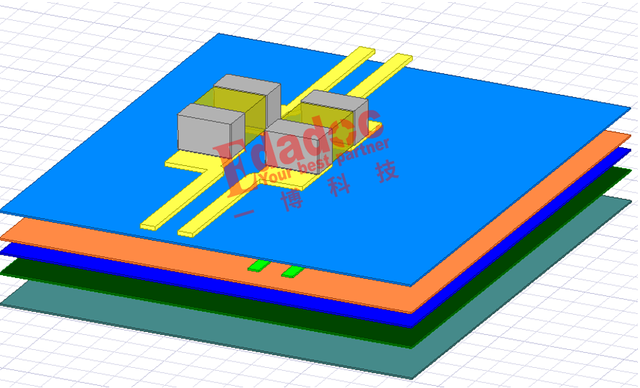

今天要分析的就是它!AC耦合電容在表層,然后高速走線在L3層,中間L2層是地平面的這種情況。那就回到了題目和摘要說的問題了,根據(jù)電磁場理論,電容在表層,走線在L3層,如果中間的L2層是個完整的參考平面的話,表層的電容及走線和L3層的走線之間是不存在串?dāng)_的,因為電磁場沒有交集。

但是凡事都不能往理想的情況去想。理論肯定是對的嘛,關(guān)鍵重點是要L2層是個“完整”的參考平面,什么是完整呢?就像上面那個電容的3D模型圖,L2層的平面就是完整了啊,所以電容和走線就是沒串?dāng)_啊!但是串?dāng)_是沒了,只不過讓電容鏈路的信號質(zhì)量承擔(dān)了所有。

我們知道,電容結(jié)構(gòu)本身的焊盤比較寬,那么阻抗如果參考L2層那么近的話,阻抗肯定是低的,就像上面這個模型一樣,如果只參考L2層地平面的話,阻抗只有60歐姆左右。對,你沒聽錯,100歐姆的差分,電容位置的阻抗只有60歐姆!

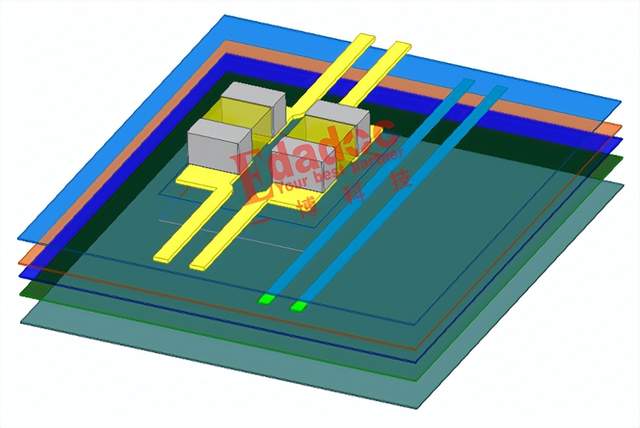

那當(dāng)然不行啊!這樣反射很大,信號質(zhì)量估計差到?jīng)]邊啦!所以我們針對電容結(jié)構(gòu)去優(yōu)化的最佳方案就是挖空電容下面的參考層,例如通過仿真給出以下的一個反焊盤挖空方案,這樣的話,電容結(jié)構(gòu)的阻抗就能做到90歐姆以上了!

完美!電容結(jié)構(gòu)本身的信號質(zhì)量優(yōu)化得杠杠的了!但是問題不就來了嘛,L2層由于挖空了地平面,變成了不完整的平面了,這樣的話表層的電容和L3層的走線就不是之前的沒串?dāng)_的狀態(tài)了哦。從下圖可以發(fā)現(xiàn),表層的電容和L3層的走線就會通過L2層的這個挖空的區(qū)域產(chǎn)生電磁場的交集,也就是會有串?dāng)_產(chǎn)生了!

但是,在設(shè)計中,這是個電容放置的密集區(qū)域,可能會有幾十對高速鏈路,也就是并排放著幾十對電容,L3層的高速線能挪開的空間肯定也不大。那我們前期去評估這種挖空case下電容和高速走線間的串?dāng)_量級就非常的有意義了,可以指導(dǎo)我們走線到底拉開多少距離能滿足串?dāng)_的要求。

以下動圖是走線在垂直方向上從近到遠(yuǎn)拉開距離的設(shè)計過程:

那我們同步也去掃描仿真的結(jié)果,從0mil(也就是貼著反焊盤邊緣)到拉開10mil垂直距離,串?dāng)_的變化如下所示:

可以看到,要是走線貼著反焊盤邊緣時,對于25Gbps的高速信號,串?dāng)_只有33dB,比較不理想。然后每拉開多2mil,串?dāng)_大概能改善5dB,是一個很不錯改善幅度。

這里其實有2個問題是值得關(guān)注的,從信號質(zhì)量的角度看,肯定就是拉開的距離越遠(yuǎn),串?dāng)_的改善越明顯,但是到底有沒有那么多垂直空間給你拉開,這個要根據(jù)這個項目的空間密度來權(quán)衡了。另外一個方面,可能大家不一定想到,那就是加工層偏的影響。一般的板廠加工的層偏誤差都會有4mil以上,尤其是高多層的情況下,這個值會更大。結(jié)合到我們今天講的這個case,有可能你在設(shè)計中是拉開了4mil的距離,但是加工層偏又會導(dǎo)致你回到0mil的串?dāng)_狀態(tài)。更極限的是,如果本身設(shè)計就是貼著反焊盤,也就是0mil的設(shè)計,那加工出來可能變成了-4mil,也就是走線之間到了反焊盤區(qū)域里面了,這樣串?dāng)_就更恐怖了。So。。。我們千萬不要忽視加工誤差的影響,選擇一個好的板廠,能給大家承諾最小的層偏誤差,這樣也能給大家的設(shè)計留出更多的裕量的哦!

| 歡迎光臨 (http://m.raoushi.com/bbs/) |

Powered by Discuz! X3.1 |