(1)熟悉QUARTUS II軟件的VHDL使用及設(shè)計流程;

(2)掌握VHDL的基本編程方法;

(3)學(xué)習(xí)基本組合邏輯門電路的設(shè)計、仿真和硬件測試。

二、實驗原理首先利用QUARTUS II建立工程項目,在工程項目中建立VHDL文件,完成4選1數(shù)據(jù)選擇器的文本編輯輸入和仿真測試等步驟,測試通過之后,在實驗儀上進行硬件測試,以驗證本實驗項目設(shè)計的功能。

三、主要儀器及耗材本實驗使用的主要儀器:PC機,實驗儀。

本實驗使用的軟件:Quartus II9.0。

四、實驗內(nèi)容和步驟1、實驗內(nèi)容

(1)用Quartus II建立工程

(2)用VHDL語言設(shè)計4選1數(shù)據(jù)選擇器

(3)用文本輸入法輸入

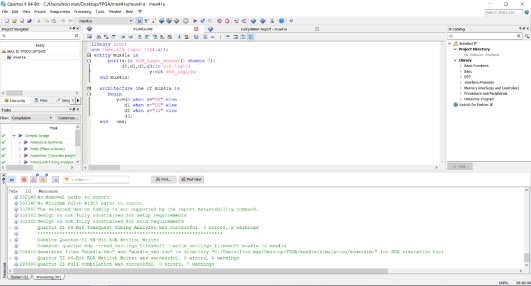

(4)編譯,改錯,直至程序編譯通過

(5)仿真,驗證所設(shè)計電路的正確性

(6)下載到實驗儀,進一步驗證所設(shè)計電路在目標(biāo)板上運行的正確性

2、實驗步驟

(1)在所使用的計算機上建立自己的文件夾(注:請建立在非C盤中);如圖1-1所示。

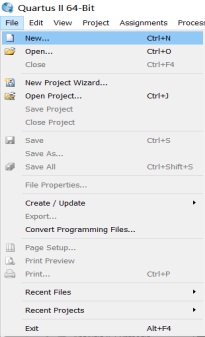

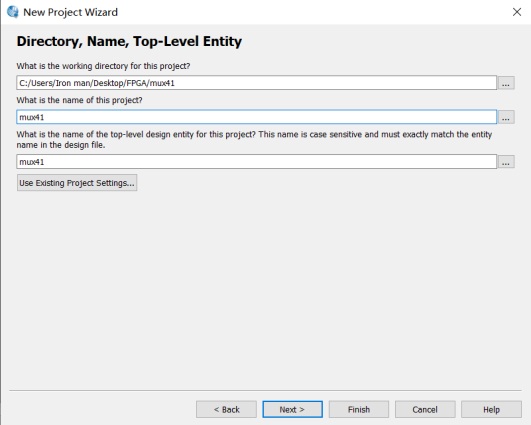

(2)打開Quartus II,選擇file-----New Project Wizard...

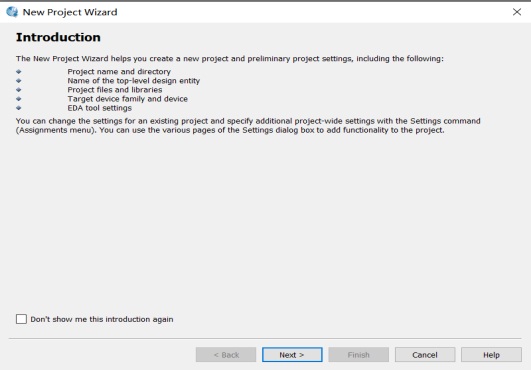

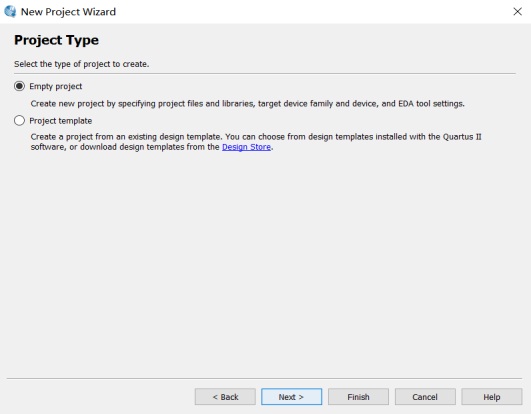

彈出如下窗口,本窗口介紹創(chuàng)建一個工程需要執(zhí)行的設(shè)置,如圖1-2、圖1-3。點擊next。建立完成工程項目,注意觀察Quartus II界面變化。

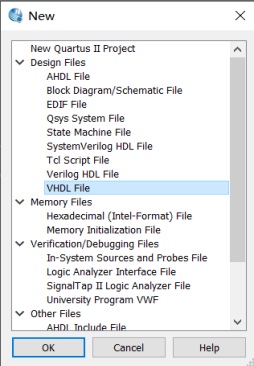

(3)單擊工具欄中的new(或菜單命令:File?New),在出現(xiàn)的對話框中選擇VHDL File,點擊OK,如圖1-7。

(6)時序仿真。

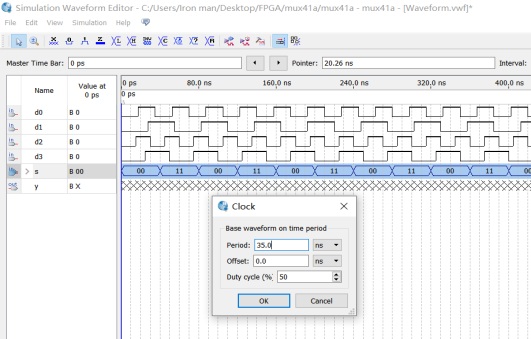

單擊new,在出現(xiàn)的對話框中選擇第二個標(biāo)簽“Other Files”,選擇“Vector Waveform File”,點擊OK。

選擇菜單View下“Utility Windows”中的“Node Finder”,出現(xiàn)“Node Finder”對話框。在“Node Finder”對話框中,上面中間的“Filter”右邊下拉列表框中選擇“Pin:all”,點擊“l(fā)ist”按鈕,將出現(xiàn)的端口信息按需要拖入波形窗口中。

設(shè)置輸入波形,保存波形文件。如需要修改仿真時間,點擊Edit菜單下的End Time。保存波形文件。

時序仿真,仔細(xì)讀仿真報告,判斷電路的正確性;如不正確,修改程序,重新編譯、仿真,直至設(shè)計的電路完全正確。如下圖。

(7)時序仿真通過之后,根據(jù)實驗儀上的芯片型號,在Quartus II工程項目中選擇對應(yīng)的芯片型號,進行適配(即將設(shè)計端口與芯片的管腳進行鎖定),重新編譯,通過之后,下載到實驗儀,進行硬件仿真驗證。

為端口選擇相應(yīng)的管腳。選擇4號5號管腳,下載成功的話,測量這兩管腳應(yīng)該一個高電平,一個低電平。

下載:在mode中選擇JTAG,如果沒有出現(xiàn)下載文件,手動選擇add file....選擇CPLDtest.pof文件。

選擇編程器:點擊Hadware Setup..彈出對話框中選擇,usb blaster,單擊close,勾選相應(yīng)配置選項,單擊start開始下載程序。進度條都100%時說明下載完成。0%到100%,本次下載用了25秒鐘,如果進度條很快幾秒鐘就到100%說明沒成功下載。最后,萬用表測量芯片管腳(4號高電平,5號低電平)。驗證程序確實下載OK。

(8)關(guān)閉工程。點擊菜單下的close project,關(guān)閉當(dāng)前工程項目。

五、實驗注意事項1、先在QUARTUS II中進行編輯、編譯、仿真測試,直到驗證結(jié)果正確為止。

2、實驗儀使用:先給實驗儀連接好電源線后,再上電,然后用數(shù)據(jù)線將實驗儀上左邊中部的電子設(shè)計下載口(JP4—ByteBlasterII)與FPGA目標(biāo)板上的JTAG Port連接起來,用下載線將實驗儀與PC的并口進行連接;再將其邊上的“下載允許”按鍵撥到“DLOAD”,再通過芯片選擇開關(guān)切換到“To_FPGA”。連接好后,即可下載進行硬件實測。

六、實驗報告要求寫出正確的程序,給出正確的仿真波形圖,并簡要說明實驗中遇到的問題及解決方法。

實驗一 基于VHDL組合邏輯電路設(shè)計.docx

(515.47 KB, 下載次數(shù): 12)

實驗一 基于VHDL組合邏輯電路設(shè)計.docx

(515.47 KB, 下載次數(shù): 12)

| 歡迎光臨 (http://m.raoushi.com/bbs/) | Powered by Discuz! X3.1 |